# Software Platforms for Modern Embedded Systems

Techniques Towards Productivity, Reliability and Scalability

# Yixiao Li

### Abstract

The increasing complexity of modern embedded systems makes software platform techniques more necessary than ever. Even the cheapest devices can have advanced connectivity now. For high-end embedded systems (e.g. autonomous vehicles), multi/many-core processors are adopted to satisfy the growing demand for computing power. Productivity, reliability and scalability are essential requirements for a software platform. In this dissertation, some major open issues are introduced at first. Three studies – EV3RT, FMP-MC, ESPROF – are then presented to shed some lights on and discuss possible solutions to them.

In the study of EV3RT, how to build a reliable RTOS-based platform meeting both realtime performance and connectivity requirements, with significantly reduced implementation effort, for Mindstorms EV3 robotics kit is explained. A dynamic module loading mechanism for static OS design is proposed to improve the productivity of development process. The performance and footprint are compared with Linux-based platforms to show the advantages for resource- and time-critical applications.

In the study of FMP-MC, a testbed for running high-performance applications on traditional multi-core RTOS is created. By a comparative analysis with Linux on a many-core processor, several bottlenecks commonly existing in RTOSes are identified and resolved. Multiple parallel applications from PARSEC are used for evaluation. The results indicate that traditional multi-core RTOS can be optimized to deliver good scalability on many-core.

In the study of ESPROF, a generic source-level profiling infrastructure for multi/manycore embedded systems is proposed. It allows user to flexibly and effortlessly create optimized tools with advanced algorithms. A scalable call graph profiler is implemented as an example, and shows much higher accuracy with very low overhead compared to existing tool in measuring benchmark application on a 36-core platform.

Besides proposed solutions to those directly addressed issues, all the studies are opensource and can provide some conceptual and practical bases for further research. The state of the art and some noteworthy trends about techniques related to software platforms for future embedded systems are also discussed.

## Acknowledgements

First of all, I would like to thank my supervisor, Prof. Hiroaki Takada, for giving me the opportunity to study in his laboratory. I also thank my advisor, Prof. Yutaka Matsubara. I would not have been able to complete studies in this dissertation without their invaluable guidance, support and advice throughout my PhD.

Special thanks to all those people who have offered help in my life, especially during hard times such as the recovery period after a surgery.

I owe a debt of gratitude to the open-source-software movement. Open-source projects formed the basis of my research. Some (e.g. Visual Studio Code from Microsoft and Markdown Monster from West Wind Technologies) also boosted my daily productivity.

Financial support from the NGK SPARK PLUG foreign student scholarship is gratefully acknowledged.

Last but not least, I thank my family and friends for the constant support, encouragement and understanding.

# **Table of contents**

| Li | st of f | igures  |                                                    | xi   |

|----|---------|---------|----------------------------------------------------|------|

| Li | st of t | ables   |                                                    | xiii |

| N  | omeno   | clature |                                                    | XV   |

| 1  | Intr    | oductio | n                                                  | 1    |

|    | 1.1     | Backg   | round                                              | 1    |

|    | 1.2     | Overv   | iew                                                | 4    |

| 2  | EV3     | RT: Re  | eal-time Software Platform for LEGO Mindstorms EV3 | 7    |

|    | 2.1     | Introdu | uction                                             | 7    |

|    | 2.2     | Overv   | iew of EV3RT                                       | 10   |

|    |         | 2.2.1   | Platform Architecture                              | 10   |

|    |         | 2.2.2   | Application Development in EV3RT                   | 13   |

|    | 2.3     | TOPP    | ERS/HRP2 RTOS Kernel                               | 17   |

|    |         | 2.3.1   | Static Configuration Approach                      | 18   |

|    |         | 2.3.2   | Kernel Object Access Control                       | 19   |

|    |         | 2.3.3   | Memory Protection Support                          | 20   |

|    |         | 2.3.4   | Extended Service Call                              | 21   |

|    |         | 2.3.5   | Task Priority Protection                           | 22   |

|    | 2.4     | Dynan   | nic Module Loading                                 | 23   |

|    |         | 2.4.1   | Dynamic Creation Extension                         | 24   |

|    |         | 2.4.2   | Design of Proposed Mechanism                       | 25   |

|    |         | 2.4.3   | Container                                          | 30   |

|    |         | 2.4.4   | Loader                                             | 31   |

|    | 2.5     | Applic  | cation Loader in EV3RT                             | 32   |

|    | 2.6     | Device  | e Drivers and Middleware                           | 34   |

|    |         | 2.6.1   | Analysis and Strategy Decisions                    | 34   |

|   |     | 2.6.2   | Reusing Linux Device Drivers                                  | 35 |

|---|-----|---------|---------------------------------------------------------------|----|

|   |     | 2.6.3   | Bluetooth Support with BTstack                                | 38 |

|   |     | 2.6.4   | File System Support with FatFS                                | 39 |

|   | 2.7 | Perfor  | mance Evaluation                                              | 40 |

|   | 2.8 | Conclu  | usions                                                        | 42 |

| 3 | FM  | P-MC:   | Analysis and Optimization of RTOS Scalability for Many-Core   | 43 |

|   | 3.1 | Introd  | uction                                                        | 43 |

|   | 3.2 | Experi  | iment Environment Overview                                    | 45 |

|   |     | 3.2.1   | TILE-Gx72 Embedded Many-Core Processor                        | 45 |

|   |     | 3.2.2   | TOPPERS/FMP Multi-Core RTOS Kernel                            | 46 |

|   |     | 3.2.3   | PARSEC Benchmark Suite                                        | 47 |

|   | 3.3 | Runtir  | me System Analysis and Optimization                           | 48 |

|   |     | 3.3.1   | OS Kernels                                                    | 48 |

|   |     | 3.3.2   | Middleware in Runtime Environment                             | 55 |

|   | 3.4 | Perfor  | mance Evaluation                                              | 59 |

|   |     | 3.4.1   | Runtime System Settings                                       | 59 |

|   |     | 3.4.2   | Blackscholes                                                  | 60 |

|   |     | 3.4.3   | Swaptions                                                     | 63 |

|   |     | 3.4.4   | Streamcluster                                                 | 63 |

|   |     | 3.4.5   | Dedup                                                         | 66 |

|   | 3.5 | Conclu  | usions                                                        | 68 |

| 4 | ESP | PROF: ( | Generic Profiling Infrastructure for Embedded Multi/Many-Core | 71 |

|   | 4.1 |         | uction                                                        | 71 |

|   | 4.2 |         | w of Existing Tools                                           | 72 |

|   |     |         | Target Embedded Systems                                       | 72 |

|   |     | 4.2.2   | Data Collection Methods                                       | 73 |

|   |     | 4.2.3   | Profiling Tools for HPC                                       | 74 |

|   |     | 4.2.4   | Profiling Tools for Embedded                                  | 75 |

|   |     | 4.2.5   | Source Code Instrumentation Tools                             | 75 |

|   | 4.3 | Requi   | rements Analysis                                              | 76 |

|   | 4.4 | -       | the Profiling Infrastructure                                  | 77 |

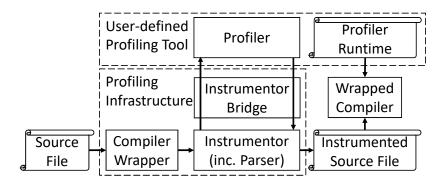

|   |     | 4.4.1   | Architecture                                                  | 78 |

|   |     | 4.4.2   | Structure of a Profiler Project                               | 81 |

|   |     | 4.4.3   | Integrating into Existing Application                         | 82 |

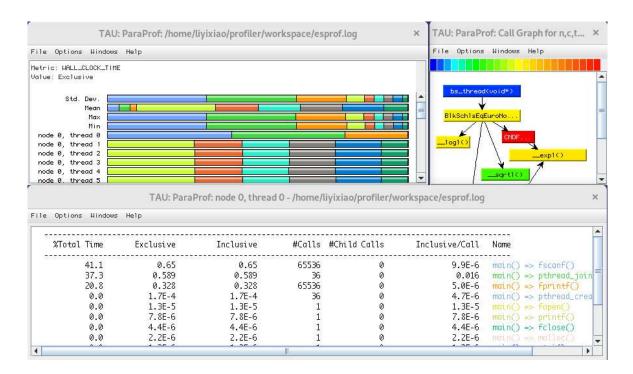

|   | 4.5 | ecg: a  | Call Graph Profiler on esprof                                 | 82 |

| Aj         | Appendix A List of Related Publications 1 |                                     |    |  |

|------------|-------------------------------------------|-------------------------------------|----|--|

| References |                                           |                                     |    |  |

|            | 5.2                                       | State of the Art and Future Trends  | 92 |  |

|            | 5.1                                       | Summary of Contributions            | 91 |  |

| 5          | Con                                       | clusions and Future Trends          | 91 |  |

|            | 4.7                                       | Conclusions                         | 90 |  |

|            | 4.6                                       | Evaluation                          | 88 |  |

|            |                                           | 4.5.2 Implementing the Profiler     | 85 |  |

|            |                                           | 4.5.1 Data Structures and Algorithm | 82 |  |

# List of figures

| 1.1  | Generalized architecture of layered software platform              | 2  |

|------|--------------------------------------------------------------------|----|

| 2.1  | Visual programming in LabVIEW                                      | 9  |

| 2.2  | Architecture of EV3RT                                              | 11 |

| 2.3  | Screenshot of EV3RT console                                        | 12 |

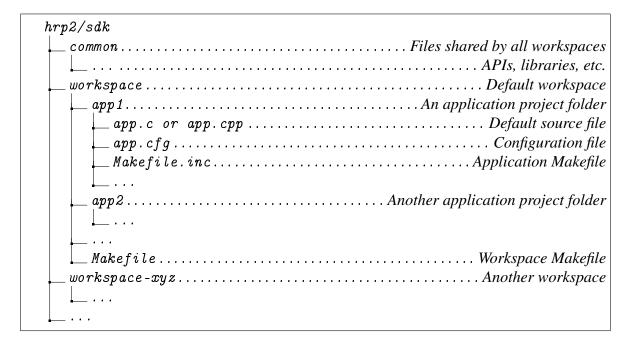

| 2.4  | Structure of the sdk folder                                        | 13 |

| 2.5  | Example of application-specific Makefile                           | 14 |

| 2.6  | Example of a configuration file                                    | 19 |

| 2.7  | Example of extended service call                                   | 22 |

| 2.8  | Proposed Dynamic Loading Mechanism                                 | 26 |

| 2.9  | Example of a module configuration table                            | 29 |

| 2.10 | Example of configuring a container and its segments                | 30 |

| 2.11 | Configuration of the application container in EV3RT                | 33 |

| 2.12 | Example of reusing Linux device driver                             | 37 |

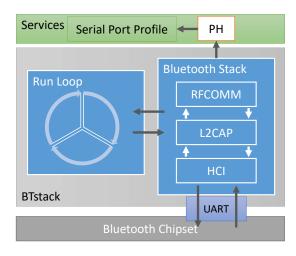

| 2.13 | Architecture of BTstack                                            | 38 |

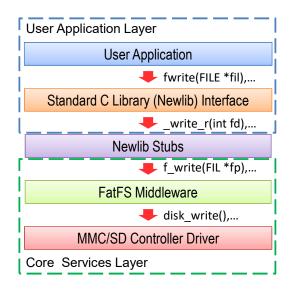

| 2.14 | Call flow of a standard file operation                             | 39 |

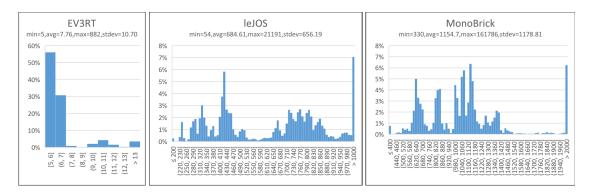

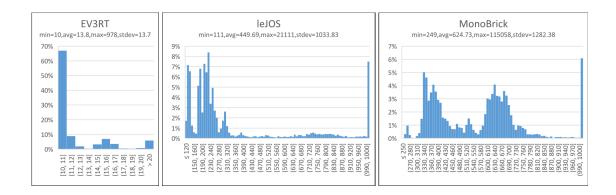

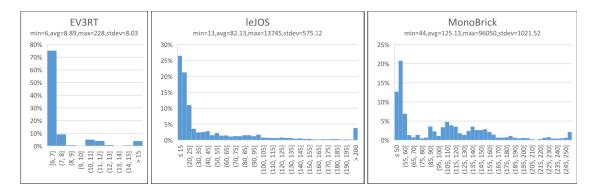

| 2.15 | Histograms of observed thread switching latency in $\mu$ s         | 41 |

| 2.16 | Histograms of motor control API's overhead in $\mu$ s              | 42 |

| 2.17 | Histograms of sensor access API's overhead in $\mu$ s              | 42 |

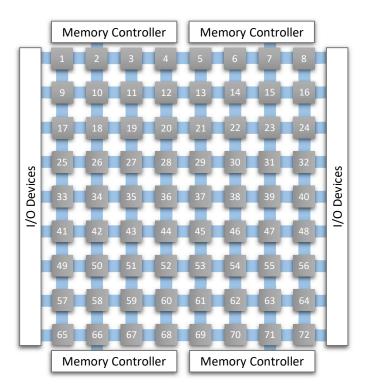

| 3.1  | iMesh NoC in TILE-Gx72 processor                                   | 46 |

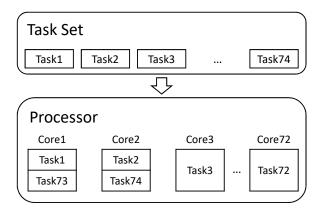

| 3.2  | Example of mapping tasks in a round-robin fashion                  | 50 |

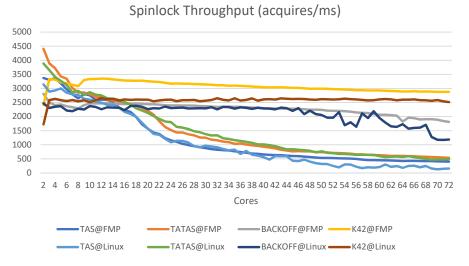

| 3.3  | Spinlock throughput of different implementations                   | 54 |

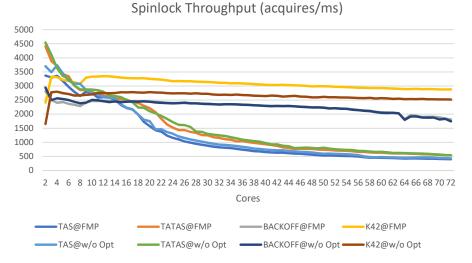

| 3.4  | Spinlock throughput in FMP with and without page optimization      | 54 |

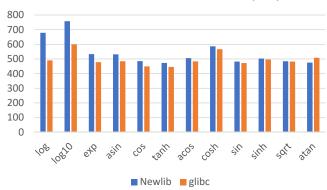

| 3.5  | Benchmark execution time of different mathematical libraries       | 57 |

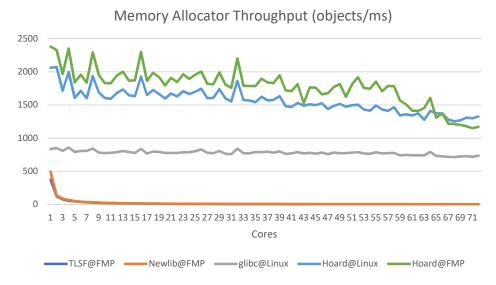

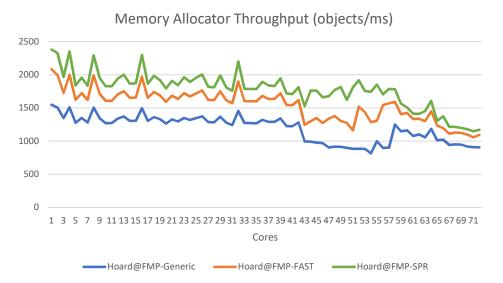

| 3.6  | Memory allocator throughput of different implementations           | 58 |

| 3.7  | Memory allocator throughput in FMP with different optimizations    | 59 |

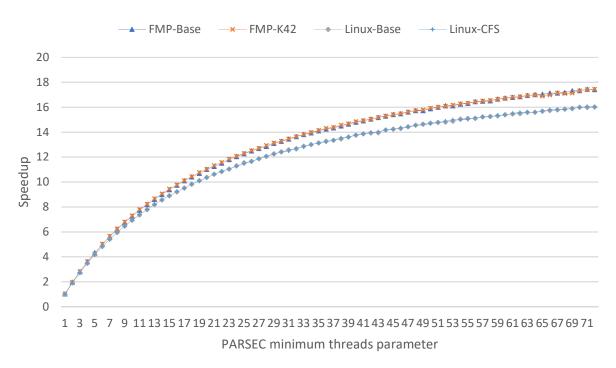

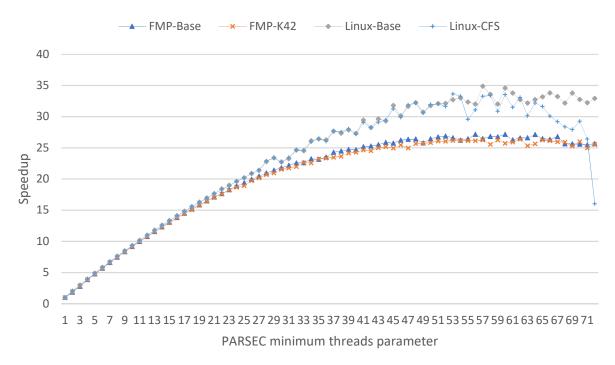

| 3.8  | Scalability of blackscholes with different runtime system settings | 61 |

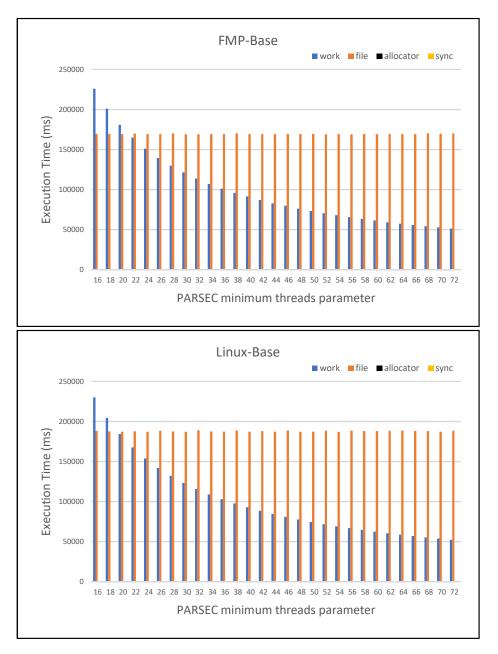

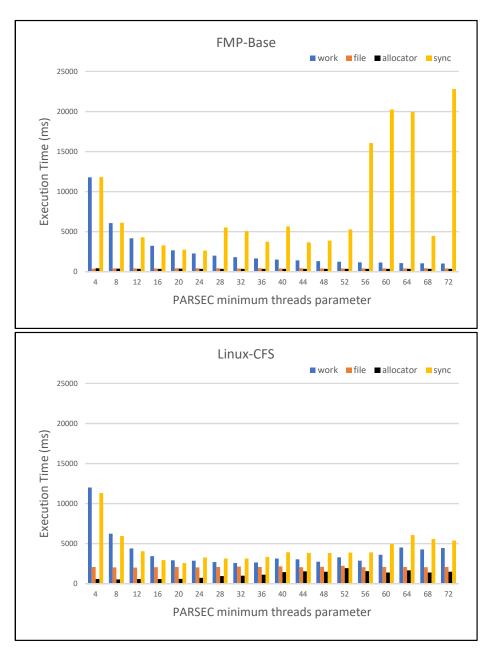

| 3.9  | Breakdown of blackscholes execution time                            | 62 |

|------|---------------------------------------------------------------------|----|

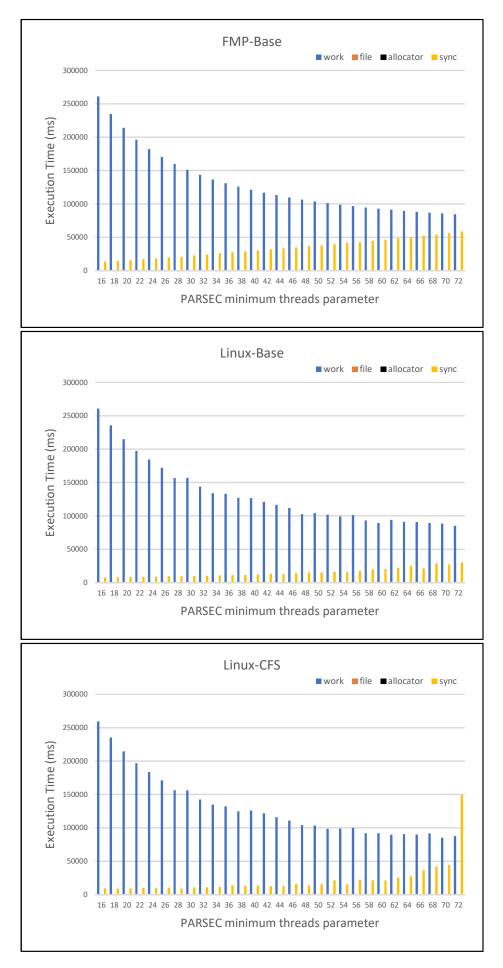

| 3.10 | Scalability of swaptions with different runtime system settings     | 63 |

| 3.11 | Scalability of streamcluster with different runtime system settings | 64 |

| 3.12 | Breakdown of streamcluster execution time                           | 65 |

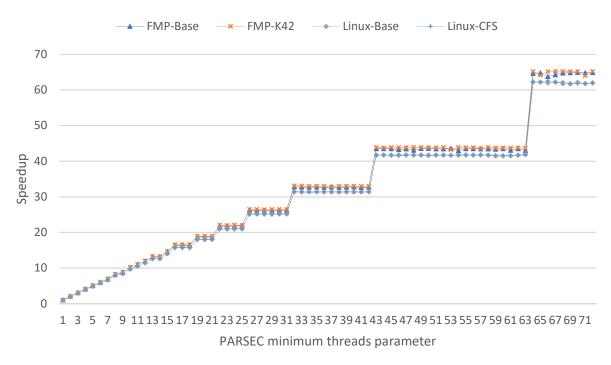

| 3.13 | Scalability of streamcluster with spin barriers                     | 66 |

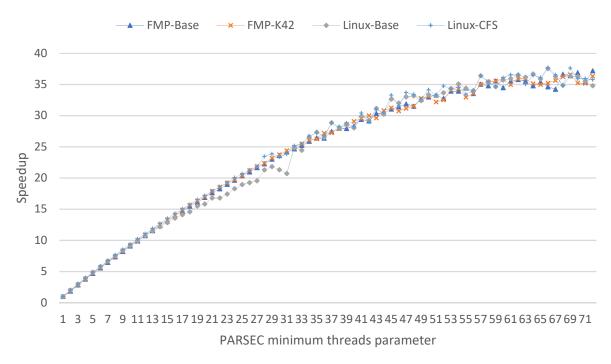

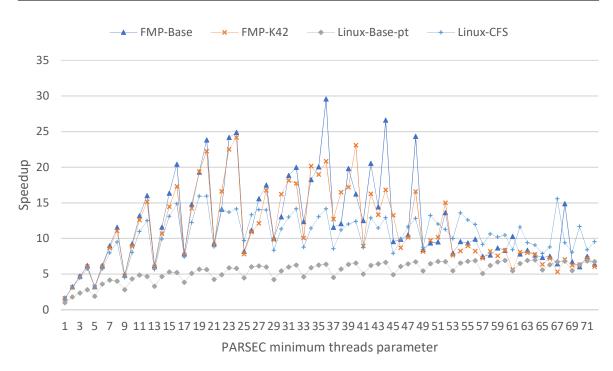

| 3.14 | Scalability of dedup with different runtime system settings         | 67 |

| 3.15 | Breakdown of dedup execution time                                   | 68 |

| 4.1  | Architecture of <i>esprof</i>                                       | 78 |

| 4.2  | A sample source file named foo.cpp                                  | 80 |

| 4.3  | Instrumentor knowledge for foo.cpp                                  | 80 |

| 4.4  | Example of a dummy profiler script in Python                        | 81 |

| 4.5  | CCT data structures                                                 | 83 |

| 4.6  | Python script for <i>ecg</i> profiler                               | 86 |

| 4.7  | Environment file of <i>ecg</i> for FMP-MC                           | 87 |

| 4.8  | A screenshot of ParaProf                                            | 88 |

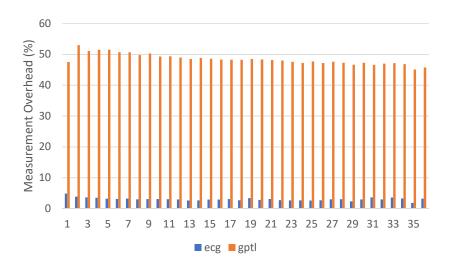

| 4.9  | Measurement overhead comparison                                     | 90 |

# List of tables

| 2.1 | Comparison of Mindstorms NXT and Mindstorms EV3                 | 8  |

|-----|-----------------------------------------------------------------|----|

| 2.2 | Software metric comparison of Mindstorms NXT and Mindstorms EV3 | 34 |

| 2.3 | Basic characteristics of EV3RT, leJOS and MonoBrick             | 40 |

| 2.4 | Execution time of HaWe Brickbench benchmark in ms               | 41 |

| 3.1 | Runtime system settings for FMP-Base and Linux-Base             | 60 |

| 4.1 | Profiles collected using GPTL                                   | 89 |

| 4.2 | Profiles collected using <i>ecg</i>                             | 89 |

# Nomenclature

#### **Acronyms / Abbreviations**

- ABI Application Binary Interface

- API Application Programming Interface

- AST Abstract Syntax Tree

- AUTOSAR AUTomotive Open System ARchitecture

- CCT Calling Context Tree

- CFS Completely Fair Scheduler

- CSL Core Services Layer

- DDC Dynamic Distributed Cache

- FMP Flexible Multiprocessor Profile

- GPOS General-Purpose Operating System

- GUI Graphical User Interface

- HPC High Performance Computing

- IDE Integrated Development Environment

- IMA Integrated Modular Avionics

- IoT Internet of Things

- PIL Platform Interface Layer

- PWM Pulse Width Modulation

- RTE RunTime Environment

- RTOS Real-Time Operating System

- SDK Software Development Kit

- SLOC Source Lines Of Code

- SoC System On a Chip

- SSH Secure SHell

- TCB Trusted Computing Base

- TEE Trusted Execution Environment

- TLSF Two-Level Segregated Fit

- UAL User Application Layer

## Chapter 1

# Introduction

## 1.1 Background

An embedded system is a dedicated computer system to perform specific functions. Typical examples of applications include consumer electronics, vehicle control and factory automation. Many tasks in these systems interact with the physical environment and thus have real-time constraints. For embedded systems targeting mass production, the manufacturing cost of hardware is a crucial concern. Energy efficiency is also important because they often run on batteries. Therefore, software implementations in embedded systems are highly optimized for low overhead and small footprint to use a minimum amount of hardware resources.

The size and complexity of software in embedded systems can vary a lot for different application domains. Applications for low cost embedded devices are usually built on a lightweight RTOS (Real-Time Operating System) kernel (e.g. FreeRTOS[4], TOPPERS[131]). Many extremely resource-constrained devices even use bare-metal applications, which directly run on the hardware without any underlying kernel, to eliminate the footprint of RTOS kernel [33]. On the other hand, in industries like avionics and automotive, software can be very large in scale. For example, a Boeing 747 airliner has tens of millions of SLOC, and system for a recent car can even exceed 100 million SLOC [94].

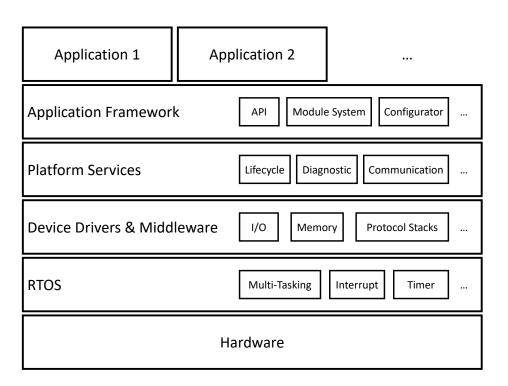

For large-scale embedded systems, platform-based design [110] has been applied for years as a powerful methodology to cope with the ever-increasing pressure on development cost and time-to-market. Famous examples include IMA [47] for avionics and AUTOSAR [27] for automotive. While the definition of "software platform" is very loose and domain-dependent, a generalized overview is shown in Fig. 1.1.

The development of applications is based on a framework which usually includes domainspecific APIs, management system for software modules/components and common toolsets

Fig. 1.1 Generalized architecture of layered software platform

(e.g. code configurator, compiler, analyzer). A module system specifies the boundary of an application to build and deploy. It may also allow developers to define interfaces between software packages to support component-based development [13]. In most cases, application modules are statically linked with the platform as a monolithic image. The framework should have stable and versioned specifications to enable the maintainability and reusability of applications.

Device drivers and middleware provide interfaces to control the hardware. They should be implemented upon the RTOS in order to cooperate with other components using the kernel services. Low-level hardware abstractions (e.g. interrupt controller and timer) are considered as a part of the RTOS rather than device drivers in this figure.

Platform must provide necessary services supporting the framework functionalities. For instance, it receives (and checks) a domain-specific API invocation and then uses device drivers to accomplish the request. It manages the resources allocated to each application, and decides the lifecycle of (i.e. how and when to start/terminate) an application. If multiple applications can run at the same time, it should also provide a mechanism for communication. Over-the-Air updating, diagnostics and network manager are some examples of other possible platform services.

Modern embedded systems can accomplish much more complex tasks than before, benefiting from rapid advances in technology. Ubiquitous connectivity and multi/many-

core architecture have gained significant importance in the industry. The hardware cost of supporting connectivity has drastically dropped (e.g. \$2 SoC with WiFi [112]). It makes the IoT (Internet of Things) concept, which delivers better/smarter services by connecting more physical objects to the internet, feasible. Further, for high-end embedded systems (e.g. autonomous vehicles), multi/many-core processors are adopted to satisfy the increasing performance requirements. Besides traditional real-time applications, these systems also tend to include high-performance parallel applications.

The increasing complexity of embedded systems makes software platform techniques more necessary than ever. Meanwhile, it brings many new challenges and questions, especially in terms of productivity, reliability and scalability. Some of the major ones are listed as follows.

- (1) Productivity: Many recent mid-range and high-end devices are capable of running Linux-based platforms out-of-the-box. What are the costs and benefits to build and use RTOS-based platforms? Are they still appealing to those hardware systems?

- (2) **Reliability:** Existing IoT-oriented platforms mainly focus on extending connectivity. For applications like industrial IoT, the reliability is as much as, if not more, important. How to enhance the reliability of a platform?

- (3) **Productivity, Reliability:** Software updating has become a key feature for connected devices to remove bugs and improve functionality. For some applications, such as safety-critical ones, system reboots can be expensive, and thus dynamic updating is desirable. Meanwhile, in existing systems, static design (e.g. allocating kernel objects at compile time) is a popular approach to reduce resource usage and improve real-time performance. Can updating in a static OS-based platform be less disruptive?

- (4) **Scalability:** Most current embedded multi-core processors only have several cores. Therefore, traditional platforms are not designed to run high-performance parallel applications. Potential bottlenecks may be triggered and cause poor performance as the number of cores increases. In order to deliver good scalability, it is vital to identify and deal with those problems.

- (5) **Productivity, Scalability:** Performance analysis tools are essential for finding applicationinternal bottlenecks in parallel computing. Existing tools for HPC-oriented platforms are not suitable for embedded systems, especially in terms of resource usage and overhead. Meanwhile, creating new analysis tools is not easy due to the diversity in hardware and software architectures.

### 1.2 Overview

This dissertation consists of three contributions to shed some lights on and discuss possible solutions to those open issues.

In Chapter 2, issues (1) (2) (3) are addressed in a specific, yet representative, context: software platforms for LEGO Mindstorms EV3 robotics kit. EV3 has significant improvements in performance and connectivity compared to its predecessor (Mindstorms NXT), and is the first model supporting Linux-based platforms. While RTOS-based platforms are usually advantageous for real-time applications, creating a new platform is difficult and costly due to the increased complexity. No RTOS for NXT has supported protection functionalities, but the reliability of RTOS for EV3 must be enhanced. Otherwise, the software scale growth will make the platform much more susceptible to failure. In traditional development process, the platform and application are statically linked as a monolithic image, and thus updating requires reboot and drops all connections. Meanwhile, robot control applications, especially to users attending competition events, will be updated very frequently during development. Therefore, dynamic updating is an essential requirement for the productivity.

*EV3RT*, the first RTOS-based software platform for LEGO Mindstorms EV3 robotics kit, is proposed. It has a representative architecture for modern systems with both realtime performance and connectivity requirements. Policies, built upon its static kernel with protection functionalities, are applied to improve reliability. A dynamic module loading mechanism for static OS design is proposed to support rebootless application updating. By techniques like reusing device drivers from stock firmware, the implementation cost has been greatly saved. Performance evaluation results show that EV3RT can deliver highly predictable performance with very small overhead and footprint compared to Linux-based platforms.

In Chapter 3, issue (4) is addressed in an empirical way. A testbed allowing existing RTOS to run parallel applications on many-core processor is highly desirable and must be created at first. Comparing the testbed with Linux-based platform optimized for HPC is very likely to give us valuable hints about scalability problems in RTOS. To evaluate the effectiveness of our solutions, multiple real applications, in addition to microbenchmarks, should be used.

*FMP-MC*, a prototype platform for many-core embedded systems, is proposed. It is based on a traditional multi-core RTOS but includes necessary runtime system for running high-performance applications on a 72-core processor. Several bottlenecks in it are identified and methods to avoid them are proposed, through a comparative analysis between FMP-MC and Linux-based runtime system. PARSEC, a popular benchmark suite composed of

parallel applications, is used to evaluate the performance. The results show that, after proper optimization, FMP-MC can deliver better scalability than Linux in many cases.

In Chapter 4, a preliminary study towards issue (5) is described. Since traditional RTOSbased platforms are not for parallel applications, performance analysis tools barely exist. We have to begin by reviewing conventional methods and conducting requirements analysis. Some common obstacles before further research should be addressed. It is desirable to implement a proof of concept to evaluate our proposal.

*ESPROF*, a generic source-level profiling infrastructure, is proposed. In the HPC domain, large monolithic profiling tools are preferred. For multi/many-core embedded systems, after discussing their characteristics and existing techniques, we believe that multiple small tools are much more suitable. ESPROF allows users to effortlessly create new tools and also provides flexibility for optimization. A scalable and optimized call graph profiler is developed as an example. It shows much higher accuracy with very low overhead compared to existing tool, in the evaluation of measuring parallel application.

Finally, in Chapter 5, we conclude this dissertation and discuss the state of the art and some noteworthy trends about techniques related to software platforms for future embedded systems.

## Chapter 2

# **EV3RT: Real-time Software Platform for LEGO Mindstorms EV3**

### 2.1 Introduction

Mindstorms [73] has become one of the most popular series of robotics development kits since it was first released by LEGO Inc. in 1998. A Mindstorms kit consists of a programmable brick computer called intelligent brick that controls the whole system, and a set of modular sensors, motors and LEGO blocks that allow users to build robots flexibly. Many reallife embedded systems can be modelled with Mindstorms robots, and thus they are used as important tools in researches [71, 17] and college education like real-time control and artificial intelligence [26, 64]. Robotics competitions such as World Robot Olympiad [140] and RoboCup Junior [124] also utilize the Mindstorms robots.

LEGO Mindstorms EV3 (or just the EV3) [135] is the third and the latest (as of writing) generation of Mindstorms series. It supports many new features and is much more powerful than its predecessor, the LEGO Mindstorms NXT [45] series, as shown in Table 2.1.

The standard software platform of EV3, however, has some disadvantages when developing applications with real-time requirements. It consists of an integrated development environment (IDE) and a Linux-based firmware. The IDE is based on LabVIEW [90] which uses a visual programming language as shown in Fig. 2.1. It is proprietary software with very limited extensibility. While it is friendly to beginners of computer programming, users who are already familiar with common programming languages like C or C++ may find it difficult to develop complex programs in this IDE. Multitasking features such as preemptive scheduling and synchronization are also unsupported. The Linux-based firmware (codename: lms2012) includes a graphical user interface (GUI) program to operate the intelligent brick

|             | Mindstorms NXT | Mindstorms EV3    |

|-------------|----------------|-------------------|

|             |                |                   |

| Processor   | ARM7@48MHz     | ARM9@300MHz       |

| Coprocessor | Atmel AVR@8MHz | n/a               |

| ROM         | 256KB          | 16MB              |

| RAM         | 64KB           | 64MB              |

| Sensors     | Analog, I2C    | Analog, I2C, UART |

| Motors      | Up to 3        | Up to 4           |

| Display     | 100×64 LCD     | 178×128 LCD       |

| SD card     | n/a            | microSD (SDHC)    |

| Bluetooth   | v1.2           | v2.1 + EDR        |

| USB device  | 12Mbps         | 480Mbps           |

| USB host    | n/a            | 12Mbps            |

| WiFi        | n/a            | USB dongle        |

Table 2.1 Comparison of Mindstorms NXT and Mindstorms EV3

and a virtual machine-based runtime, which takes a long time to boot up and has a huge memory footprint. Application will be compiled into an intermediate representation (a.k.a bytecode) to be executed in the virtual machine. The overhead and unpredictable performance of Linux kernel and virtual machine can not provide real-time guarantees. There are some other software platforms such as leJOS EV3 [123] and MonoBrick [120], which support developing in Java or C#. However, they also use Linux and have their own runtime, and thus the disadvantages of lms2012 still remain.

In this chapter, EV3RT, a real-time software platform to overcome above disadvantages, is presented. It is the first RTOS-based platform for EV3 to our knowledge and especially suitable for developing applications with hard real-time requirements such as balancing a two-wheeled robot [42]. Soft real-time and generic applications, including those for IoT devices or just entertainment, are also likely to run faster and smoother on EV3RT with its low-overhead APIs. ET Robocon (short for Embedded Technology Software Design Robot Contest) [60], a popular robot competition in Japan, has selected EV3RT as one of its officially supported platforms. Many participating teams of ET Robocon are using EV3RT to make their robots accomplish the assigned tasks more stably and precisely. Main features of EV3RT are listed as follows:

**TOPPERS/HRP2 static RTOS kernel**[129]. As an extended version of TOPPERS/JSP kernel, which is used by a popular RTOS-based platform for NXT called nxtOSEK/JSP [31], it can provide backward compatibility as long as many new features with guaranteed real-time performance.

**Programming in C and C++**. Applications can be compiled and run as native code so the overhead of virtual machine is completely eliminated.

Fig. 2.1 Visual programming in LabVIEW

**High reliability with enhanced protection**. The base system of EV3RT is protected so it will not be affected by defects in user applications, which makes the debugging effortless for a large-scale embedded software platform like EV3RT.

**Easy-to-use and low-overhead APIs**. Users can easily develop applications with realtime requirement and need not learn the complex implementation details of various device drivers.

**Dynamic application loading**. A static RTOS generally requires the system to be rebooted when the application is updated. In the case of EV3, developers have to reset the intelligent brick and reconnect network such as Bluetooth every time after modifying an application, which will waste lots of time, especially when developing robot control applications which are usually updated frequently to adjust control logic and parameters. To solve this problem, EV3RT provides a loader for the static TOPPERS/HRP2 kernel, which allows the dynamic updating of application without reboot.

**Bluetooth and USB device support**. Connectivity technologies are important in many scenarios, such as creating interactive applications or modeling an IoT device. Helpful features like uploading application wirelessly are also supported.

**Ultra-fast boot process**. The slow startup is one of the most annoying problems for EV3 developers using Linux-based platforms. Meanwhile, it only takes about 2 seconds for EV3RT to boot up.

**Very small memory footprint**. Storing or caching data in memory as possible is a common technique to improve performance and reduce latency. More than 95% of total memory can be used by applications on EV3RT.

**Complete open source platform**[44, 43]. Since Mindstorms robots have been used in so many different ways, the standard features and behaviors of EV3RT may not fit some users' needs. In that case, users can freely modify any part of EV3RT as all the source code is available.

**Extendable software architecture**. The hardware of EV3 itself is extendable by connecting devices like third party sensors. Supporting of those devices can be easily implemented with the flexible architecture provided by EV3RT.

The rest of this chapter is organized as follows. An overview of EV3RT is given in Section 2.2 at first, by describing its architecture and usage. In Section 2.3, TOPPERS/HRP2 kernel, the RTOS of EV3RT, is explained, focusing on applying its protection functionalities to make EV3RT more reliable. A dynamic module loading mechanism for static OS design is proposed in Section 2.4, in order to implement the application loader for EV3RT. We then introduce some implementation techniques such as reusing Linux device drivers in Section 2.6. The performance of EV3RT is evaluated and compared with existing software platforms in Section 2.7. Finally, the chapter is concluded in Section 2.8.

### 2.2 Overview of EV3RT

EV3RT is a developer-friendly open source software platform for real-time applications. In this section, we first give an overview of EV3RT through explaining its architecture. Thereafter, how to develop application with EV3RT in practice is also briefly described.

### 2.2.1 Platform Architecture

Application in EV3RT can be developed and built in two modes: dynamic loading mode and standalone mode. In dynamic loading mode, a base system with application loader is running on the intelligent brick. Application is separately built as a module (in ELF file format [87]) which can be dynamically loaded from micro SD card or Bluetooth and then executed under non-privileged mode on the base system. On the contrary, application in standalone mode will be compiled and linked together with the whole platform, to generate a boot image supported by the EV3's bootloader U-Boot [38]. Both modes have their own merits. Application in dynamic loading mode can be updated without rebooting EV3, which makes the development process very smooth. Its building is also much faster than in standalone mode since compilation of the whole platform is avoided. Robot control applications are usually updated frequently to adjust control logic and parameters, and thus we highly recommended dynamic loading mode to be used. On the other hand, application

Fig. 2.2 Architecture of EV3RT

in standalone mode can be directly booted by EV3 and executed under both privileged mode and non-privileged mode. It is useful for building a platform or firmware as developer has full access to RTOS kernel and hardware resources in this mode. In fact, the base system of dynamic loading mode itself is an application in standalone mode. mruby on EV3RT + TECS [127], a platform for programming EV3 in mruby, is also developed in this mode.

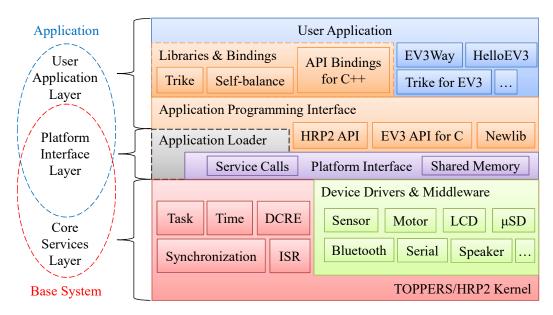

EV3RT uses a layered architecture that decouples user application from the infrastructure software as shown in Fig. 2.2, in order to achieve high flexibility, reliability and extensibility. This architecture is mainly applied to dynamic loading mode but can also be considered as a reference model for standalone mode. It consists of three layers as follows:

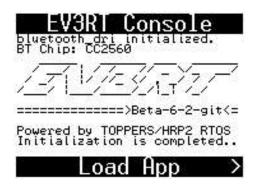

**Core Services Layer**: This layer is to provide services needed by applications and monitor the running application. It mainly consists of TOPPERS/HRP2 kernel, device drivers and middleware. TOPPERS/HRP2 kernel is a static RTOS kernel with protection functionalities. EV3RT uses it to provide system services with high reliability. Potential defects and bugs in user application (e.g. illegal memory access) will not harm the platform. Instead, they are monitored and handled by this layer and will be logged to provide information for debugging. Device drivers and middleware are modules to support various features of EV3, such as PWM (pulse-width modulation) motor control and file system. They are mainly running under privileged mode since they usually wish to manipulate hardware devices directly. EV3RT console, a user interface for selecting application to launch or viewing system logs as shown in Fig. 2.3, will show at startup after all services have been initialized.

Fig. 2.3 Screenshot of EV3RT console

Platform Interface Layer: This layer acts as an interface between core services layer (CSL) and user application layer (UAL). It specifies a list of functions that must be implemented in CSL. These functions are wrapped as service calls so that they can be called from user application which runs under non-privileged mode. There are some service calls to obtain the pointer of a shared memory area. Shared memory can be used as a simple interface to eliminate the overhead of calling the same service call repeatedly. Examples of shared memory include read-only sensor data and read-writable LCD frame buffer. Data structures and macros shared between CSL and UAL are also defined in this layer. User applications are only dependent on this layer so they can be compiled and linked as loadable modules without any detail and code of CSL. Even if implementation of CSL changed a lot, modifications to source code of UAL are unnecessary as long as this layer does not change. Therefore, platform interface layer can be considered as the application binary interface (ABI) of EV3RT and is given a version number called PIL version. This layer also includes an application loader which can be used to update the running application dynamically. On launching an application, the loader checks the PIL version of the base system and the application at first to make sure they are compatible (with the same version). The running application can be manually terminated using EV3RT console, and if it is crashed, the loader will automatically unload it.

**User Application Layer**: This layer consists of software components for building user applications and the user application itself. APIs for C language are provided, which will be introduced later in the next subsection. Runtime and API bindings for C++ have been implemented to support object-oriented programming. In addition, libraries for common robot functionalities such as self-balancing are also available. Some sample applications are included to help developers get started with EV3RT. All code in this layer runs under non-privileged mode inside a determined protection domain called TDOM\_APP, which will

Fig. 2.4 Structure of the sdk folder

be explained later in Section 2.3. Currently, only one user application can be running at the same time on EV3RT.

### 2.2.2 Application Development in EV3RT

Users can develop applications for EV3RT under Linux, Mac OS X or Windows. EV3RT uses GNU Arm Embedded Toolchain [11] for compiling. All the required software packages can be easily installed by following the guide on our website [44, 43]. Installation of EV3RT to the intelligent brick can be done by just putting boot image of the base system, which can be built with one single command, into the root directory of EV3's microSD card. In this subsection, some important information about developing applications in EV3RT are described.

### 2.2.2.1 Application Project Management

In EV3RT, user application projects are managed inside the sdk (short for software development kit) folder. The sdk folder includes a common folder holding common files such as source files of APIs and libraries, a default workspace folder named workspace and optional workspace folders which can be created by users, as shown in Fig. 2.4. A workspace folder is a folder used to hold multiple application projects. Each application project corresponds to

```

APPL_COBJS += balancer.o \

balancer_param.o

APPL_CXXOBJS +=

SRCLANG := c++

ifdef CONFIG_EV3RT_APPLICATION

# Include libraries

LDIR = $(EV3RT_SDK_LIB_DIR)

include $(LDIR)/libcpp-ev3/Makefile

endif

```

Fig. 2.5 Example of application-specific Makefile

a dedicated folder under some workspace folder. All the sample applications can be found in the default workspace.

With the workspace feature, application projects can be managed in an easy way. A new application project can be simply created by duplicating a existing project folder with a new name. Deleting a project is also straightforward: just remove the folder. An application can be built in two modes, as mentioned above, with its folder name. For example, for an application project folder named app1, developer can build it in dynamic loading mode by executing make app=app1 command under its workspace folder. After building successfully, a loadable module named app will be generated. Further, developer can also use make img=app1 to build it in standalone mode. In that case, a boot image file named uImage will be generated.

An application project has three files by default, app.c (or app.cpp when developing in C++), app.cfg and Makefile.inc. app.c (or app.cpp) is the default source file of an application which will be compiled automatically. app.cfg is the configuration file of an application. An application can be built in dynamic loading mode, only if all kernel objects defined in app.cfg belong to the predetermined application protection domain TDOM\_APP. Makefile.inc is the application-specific Makefile. Application build configuration such as source files, libraries, programming language can be customized by modifying this file. See Fig. 2.5 for an example of Makefile.inc.

#### 2.2.2.2 Development Process

The process to develop an application in standalone mode is listed as follows.

- 1. Power on the intelligent brick

- 2. Write code for the application

- 3. Generate the boot image uImage

- 4. Connect EV3 to PC with a USB cable

- 5. Copy uImage to the root of the microSD card

- 6. Restart the intelligent brick

- 7. The new application will get executed

- 8. Application needs modification, go to step 2

It should be noted that every time the application is modified, it is required to reboot the EV3 brick and write the microSD card with a PC. This procedure is a bit annoying and, if the application uses Bluetooth, the need of reconnection will make it even worse. Therefore, the standalone mode is not recommended except for developing a firmware or platform.

Developing an application in dynamic loading mode can be much more smooth. After the EV3 is booted, EV3RT console will show up on the display. Developers can use the loader in EV3RT console to receive and execute a new application wirelessly transferred from Bluetooth. Besides, applications can also be put into microSD card for execution via USB. If an application is running, user can press the back button for about 0.5 second to show the EV3RT console to terminate it and load a new application. The process is listed as follows.

- 1. Power on the intelligent brick

- 2. Write code for the application

- 3. Generate the loadable application module

- 4. Upload application via Bluetooth or USB

- 5. Start the new application

- 6. Application needs modification, go to step 2

#### 2.2.2.3 APIs for User Application

EV3RT currently provides three types of APIs as follows:

**TOPPERS/HRP2 Kernel API**: This API allows user applications to access RTOS services provided by HRP2 kernel. It includes  $\mu$ ITRON-like [132] static APIs and service calls, whose details are described in the TOPPERS new generation kernel specification[128]. Static APIs are used in the configuration file to configure the kernel objects of an application statically. On the other hand, service calls, which may be called system calls in other operating systems, are used in source files to request services at run time. In the HRP2 kernel specification, cyclic handlers can be only created in the kernel domain, which run in interrupt context under privileged mode without protection. Since cyclic handlers are also very useful in user applications, EV3RT extends the original kernel API with user domain cyclic handler functionality.

C/C++ Standard Library: Newlib[103], a C/C++ standard library implementation for embedded systems, has been ported to EV3RT. With the standard library, users can develop applications for EV3RT as easily as developing a normal C/C++ application. The support of dynamic memory management is required for most functions in Newlib. However, the default memory allocator in Newlib only supports one single heap, which is not compatible with the protection model of HRP2 kernel, and can not provide any real-time guarantee. We replaced it with the TLSF (Two-Level Segregated Fit) memory allocator [85], a memory allocator designed for real-time embedded systems. Since memory objects in HRP2 kernel are configured statically, a fixed-size memory pool is preallocated for Newlib. EV3RT also integrates communication services into the standard file operations. Special files for communication devices such as Bluetooth or serial port can be obtained. Developers can use these files to do communications just like accessing a file, by calling functions such as fprintf() and fgetc().

**EV3RT C Language API**: This API provides C language functions to support hardware devices such as sensors and other platform-specific features. Since it is used to control the robot actually, most of its functions provide high real-time performance, except those involving microSD card operations. The supported devices and features are listed as follows:

- EV3 brick (buttons, LED, LCD and speaker)

- Memory file and microSD card

- Bluetooth and serial port

- Servo motors and rotary encoder

• Various sensors (ultrasonic, color, etc.)

These APIs allow users to develop applications easily without any knowledge about the implementation details of core services layer (e.g. device drivers) in EV3RT. If a developer wants to access device drivers (including middleware) directly, the standalone mode must be used, since device drivers run under the privileged mode. In that case, the developer will also need to learn the usage of device drivers (for example, from their documents).

Besides above APIs, optional static libraries like API bindings for C++ are also available.

#### 2.2.2.4 Sample Applications

Several sample applications come with EV3RT to help developers get started. Two representative samples are introduced as follows:

HelloEV3 is a program which can be used to test the features of EV3RT thoroughly. It provides a simple GUI which can be operated with buttons on the intelligent brick. This graphical menu contains tests for all functions provided by EV3RT C language API and itself is also implemented with those functions. Further, user is allowed to reconfigure the connection of devices such as sensors and motors dynamically, without recompilation or reboot. With this sample, the implementation of EV3RT can be checked easily and developers can learn how to use EV3RT APIs by referring to its source code.

EV3Way is a sample application to control a two-wheeled self-balancing robot. The researches on two-wheeled self-balancing robot (a.k.a two-wheeled inverted pendulum mobile robot) have gained momentum over the past decades and shown that high real-time performance is required [136]. This application is developed by the executive committee of ET Robocon in C++ to control a robot called EV3Way-ET. The reference construction of EV3Way-ET is available on GitHub [42]. There are two tasks, the balancing task and the communication task, in this application. The balancing task runs in a high priority to control the robot with the self-balancing algorithm and the communication task runs in a lower priority to communicate with user via Bluetooth. Both of the tasks can work stably, which shows that EV3RT is suitable for developing applications with high real-time requirements.

### 2.3 TOPPERS/HRP2 RTOS Kernel

TOPPERS/HRP2 kernel (or just HRP2 kernel) is used by EV3RT as its RTOS kernel. It is a  $\mu$ ITRON-like [132] open source RTOS kernel created by the TOPPERS project [129]. HRP2 is short for High Reliable system Profile version 2, and by the way the first version of

HRP kernel has been adopted by the HII-B rockets [59] and proven its excellent real-time performance and reliability.

Since nxtOSEK/JSP [31], a popular RTOS platform for NXT, also uses RTOS kernels from the TOPPERS project, developers of NXT should find it easy to migrate to EV3 with EV3RT. Aside from the consideration of migration, the most important reason for choosing HRP2 kernel is that it is a static RTOS supporting various protection functionalities. Mindstorms EV3 is a relatively large-scale embedded system, and if its software platform is not protected, a bug in user application may easily break the whole platform, which makes debugging very difficult.

In this section, we focus on explaining how features of HRP2 kernel are applied to make EV3RT a reliable software platform. For a thorough description of HRP2 kernel, check the TOPPERS new generation kernel specification [128].

### 2.3.1 Static Configuration Approach

A static operating system kernel is a kernel whose kernel objects (or resources), such as tasks and memory areas, are configured at design time and statically allocated at compile time. Both EV3RT and the user applications on it are developed following this static configuration approach.

In HRP2 kernel, developers statically configure the kernel by writing configuration files using static APIs. See Fig. 2.6 for an example of configuration file. A tool called configurator will parse these configuration files. By using the parsing results as input, the configurator interprets some template files to generate necessary C source files or linker scripts. Template files are written in a template language defined by HRP2 kernel for generating files. Common template files such as generating source files for kernel objects are included in HRP2 kernel. Target-dependent template files like generating linker scripts or translation tables to support memory protection are also available for many popular targets. However, the processor of EV3 was not supported by HRP2 kernel, and thus we implemented those target-dependent template files for it.

Research has shown that a static OS design is more reliable and can provide a significantly better resilience to soft errors than the dynamic ones [58], as many potential software defects can be found during the configuration process. Besides, a static OS also tends to have higher and more stable performance and consume less memory.

```

KERNEL_DOMAIN {

/* create a system task */

CRE_TSK(MAIN_TASK, { TA_ACT, 0, maintsk, 6, 1024, NULL });

/* register a memory object */

ATT MOD("sample kernel.o");

/* define an extended service call */

DEF_SVC(SVC1, { TA_NULL, svc1_entry, 64 });

}

/* a user domain named DOM1 */

DOMAIN(DOM1) {

/* create a user task */

CRE_TSK(TASK1, { TA_ACT, 0, task1, 6, 1024, NULL });

/* register a memory object */

ATT_MOD("sample1.o");

}

/* a user domain named DOM2 */

DOMAIN(DOM2) {

/* create a user task */

CRE_TSK(TASK2, { TA_NULL, 0, task2, 6, 1024, NULL });

/* create a semaphore named SEM1 */

CRE_SEM(SEM1, { TA_NULL, 0, 1 });

/* configure access rights of SEM1 */

SAC_SEM(SEM1,{ TACP(DOM2), TACP(DOM1)|TACP(DOM2), \

TACP(DOM2), TACP(DOM2) };

}

/* define a shared memory object and set access rights */

ATA_SEC(".appheap", { TA_NULL, "RAM" }, \setminus

{ TACP_SHARED, TACP_SHARED, TACP_SHARED, TACP_SHARED });

```

Fig. 2.6 Example of a configuration file

### 2.3.2 Kernel Object Access Control

A kernel object is a system resource managed by the RTOS kernel. Kernel objects are defined in and will be generated from configuration files. Each kernel object created will be associated with an ID which can be used to access it. Tasks, semaphores and data queues are typical examples of kernel objects.

The concept of protection domain is introduced to support access control of kernel objects. There are two types of protection domains in HRP2 kernel: kernel domain and user domain. The kernel domain is unique while there can be multiple user domains. A task must belong to some protection domain to determine its permissions. Tasks in the kernel domain, called system tasks, are executed under privileged mode which has full access rights to all kernel objects. Tasks in a user domain, called user tasks, are executed under non-privileged mode with limited access rights. Other runnable kernel objects, such as alarm handlers, are always executed under privileged mode and thus must belong to the kernel domain. A protection domain is the finest granularity to grant access rights of a kernel object, which means that tasks in the same protection domain have the same access rights. By default, a kernel object allows user tasks in the same protection to access it. A non-runnable kernel object like semaphore can also be shared by all protection domains without belonging to one of them, which allows any task to access it.

In order to configure access permissions more flexibly, operations to each type of kernel objects are divided into four groups: type 1 operations, type 2 operations, management operations and reference operations. For example, in the case of semaphores, type 1 operations are for signaling, type 2 operations are for waiting, management operations are for configuring access rights, and reference operations are for acquiring status. The access rights of each group of operations for a kernel object can be configured individually.

In EV3RT, the core services layer mainly works in the kernel domain while all kernel objects in the user application layer belong to a determined user domain called TDOM\_APP. The core services layer does not allow user application to access its objects directly. Instead, service calls and shared memory defined in the platform interface layer must be used. In this way, kernel objects in the base system are protected from illegal or undesired access caused by the user application.

### 2.3.3 Memory Protection Support

Memory protection is necessary because user application can still harm the base system by operations such as writing improper values to a hardware register or changing data in the kernel, even if kernel objects are protected. What is worse, if user application breaks the file system, all data on the microSD card might be corrupted. As a high reliable RTOS, HRP2 kernel does support memory protection, with static configuration of memory objects.

In HRP2 kernel, a memory object represents an area of memory controlled by the kernel. Lots of information is associated with a memory object, including base address, size and attributes of that area, and access rights granted to protection domains. An attribute is a property that always holds regardless of which protection domain it is accessed from. For example, if a memory object has the attribute TA\_NOWRITE, its memory area cannot be written even by a system task. There are also attributes like TA\_UNCACHE to control cache behavior. If base address and size of a memory object is fixed, such as a hardware register, developer can use the ATT\_MEM static API to create it explicitly. In the case of text and data section in

an object file whose base address and size are unknown at design time, the ATT\_MOD static API can be used to generate memory objects from an object file with specified access rights. Configuring attributes and permissions for a named section defined in the source code is also supported, by using the ATT\_SEC static API with the section name. Memory objects should never overlap, otherwise an error message will show up during configuration.

Although HRP2 kernel is designed to support memory protection with both memory protection unit (MPU) and memory management unit (MMU), the ARMv5 MMU used by EV3 was not supported. In our previous work [77], we have supported the ARMv5 MMU by designing an algorithm to generate ARMv5 page tables for each protection domain, and proposed a method to optimize the TLB flushing overhead. With that optimization, ultra-low latency of context switching can be achieved.

For memory objects in the base system of EV3RT, only those defined as shared memory in the platform interface layer can be accessed from the user application layer. Most of the shared memory areas are read-only, such as sensor values and font data. Only memory areas that will not break the base system even if they are corrupted, like LCD frame buffer for user application, can be configured as read-writable shared memory. The base system has its own frame buffer which is protected from user application, for displaying interface of core services like EV3RT console. In this way, shared memory can be used as an efficient and safe method of passing data in EV3RT.

## 2.3.4 Extended Service Call

Although shared memory is very efficient, it is not enough because most user applications will also wish to execute code under privileged mode, such as using PWM device to control a motor, in a safe way. HRP2 kernel provides the extended service call functionality to support this case.

The term service call in HRP2 kernel has a similar meaning to system call in Linux. Service calls act as an interface between user domains and the kernel. This interface is essential to provide system services for a user task which is usually prevented from directly manipulating the kernel's memory. When a service call is called, it is executed under privileged mode and aware of the caller's protection domain, so illegal operations can be blocked by checking the access rights.

As a general-purpose operating system, Linux has a stable system call interface, and device drivers are abstracted as special files to be accessed with file I/O system calls. Access permissions of device drivers in Linux are also controlled using file system. Although this approach brings excellent portability, it also introduces overhead of the file system which influences the real-time performance. In HRP2 kernel, instead of providing a universal

```

KERNEL_DOMAIN {

DEF_SVC(TFN_MOTOR_COMMAND,{ TA_NULL, \

extsvc_motor_command, 1024 });

}

```

a. define extended service call in configuration file

| <pre>ER_UINT extsvc_motor_command(intptr_t cmd, intptr_t size,</pre> |  |

|----------------------------------------------------------------------|--|

| <pre>intptr_t par3, intptr_t par4, intptr_t par5, ID cdmid) {</pre>  |  |

|                                                                      |  |

| λ.                                                                   |  |

| b. implement service call in kernel domain |   |      |           |        |           |      |       |    |    |     |  |

|--------------------------------------------|---|------|-----------|--------|-----------|------|-------|----|----|-----|--|

| ercd =                                     | = | cal_ | _svc(TFN_ | MOTOR. | _COMMAND, | cmd, | size, | 0, | 0, | 0); |  |

c. call service call from user domain

Fig. 2.7 Example of extended service call

interface for device drivers, the functionality of conveniently defining new service calls, called extended service calls, is supported.

Fig. 2.7 is an example to show how extended service calls are used in device drivers and middleware of EV3RT to provide services safely. Firstly, a new service call is defined with the static API DEF\_SVC. A unique number (TFN\_MOTOR\_COMMAND in the example), called function code, is associated with each service call. The function name and stack size for the service call must also be specified. Thereafter, function body of the service call, which will be executed under privileged mode, is implemented. The function has 6 parameters: 5 of them are passed from the caller and the last one (cdmid) holds the protection domain ID of the caller. These parameters are carefully checked and an error code will be returned if any problem occurs. In user application, the cal\_svc() API is used to call a service call with its function and switch back with return value after the function has completed.

## 2.3.5 Task Priority Protection

With above policies applied, the space of base system can be protected from defects in user application. However, a user application can still influence the base system in the aspect of CPU time. HRP2 kernel uses priority-based preemptive scheduling algorithm. If a user application changes the priority of a task, for example, of an infinite loop to the highest priority, the intelligent brick will be stuck forever until a physical power-off is performed, because all tasks in the base system cannot be scheduled.

In order to solve this issue, we added the LMT\_DOM static API to the HRP2 kernel specification. This API can limit the highest priority that can be set at run time for tasks in a protection domain. It does not limit the initial priority of tasks since they can be checked during configuration, which allows developers to control the system more flexibly. EV3RT uses this API to limit task priority in TDOM\_APP, and thus the base system will not be preempted by tasks in user application.

Besides, Bluetooth service in the base system has another kind of issue on task priority. The CPU utilization of task to process Bluetooth packets depends on the speed of traffic. If the task has higher priority than user application and packets come in a very high rate, it will have a negative effect on the real-time performance of user application. On the other hand, if the task has lower priority than user application, it may never get scheduled, which will break the Bluetooth service. EV3RT copes with this issue by using a QoS (quality of service) task to control the priority of Bluetooth task dynamically. The QoS task will periodically raise the priority of Bluetooth task, which usually works in the lowest priority, to a priority higher than user application for a short time.

By default, the Bluetooth task will run in high priority for 1 ms in every 20 ms. These timing parameters are decided by an experimental approach to find the minimum required CPU resource for a relatively stable Bluetooth connection. During the experiment, a task of infinite busy loop is running as user application. The exection time of Bluetooth task in high priority is fixed at a single system tick, which is 1 ms. We then change the period to control CPU resource given to the Bluetooth task, and check whether the Bluetooth connection is stable. A connection is considered to be stable if it can complete pairing process and stay connected for over one hour. After having tested and failed with 100 ms ( $\approx 1\%$  CPU), 50 ms, 30 ms, 25 ms periods, we found that 20 ms period can provide a stable connection. Meanwhile, as a representative application with high real-time requirements, the balancing task of EV3Way has an execution time of 1 ms with 5 ms period. Therefore, Bluetooth service can be kept alive with this policy while has very limited influence on real-time performance. Users are also allowed to change the timing parameters of QoS policy or disable it as necessary.

## 2.4 Dynamic Module Loading

Dynamic updating mechanisms of software system or applications without reboot are becoming significantly necessary to reduce the time to market and development costs, with the rapid growth of the complexity of embedded systems. System reboots can be slow and disruptive and will drop all current status like network connections, which are very expensive for some safety-critical applications such as avionics [116]. For Linux-based software platforms, new applications can be transferred and executed on-the-fly within a few seconds via network protocols such as Secure Shell (SSH) [142]. While the static design of HRP2 kernel provides high robustness, the lack of dynamic updating support can be one of its main drawbacks.

In this section, we present a dynamic module loading mechanism for HRP2 kernel. The application loader in EV3RT is implemented by referring to this mechanism. Main characteristics of our original mechanism are listed as follows:

**Excellent portability**. The design of our mechanism, per se, does not depend on any specific hardware, although the motivation is to support dynamic application loading in EV3RT. It is able to support most of targets where HRP2 kernel works. Further, developers can apply it to existing systems very easily, without implementing any complex function such as dynamic memory or page table management.

**Keep it simple, static**. Our mechanism is to support dynamic updating of modules rather than to support development in a dynamic way. HRP2 kernel benefits a lot from the simplicity of its static design, especially in the aspects of performance and robustness, and our design is able to keep those advantages. All loadable modules are still configured and developed in the same way of developing a normal HRP2 application, which is static, with some restrictions and minor changes. Thus, resources required by a module are statically determined at compile time and can be checked at load time.

**Reliable and fault-tolerant**. Modules may contain bugs and could lead to incorrect or unexpected behaviors after loaded. Our mechanism has the feature to guarantee that the modules loaded will not harm the whole system. The loader will verify the configuration information of a module before loading, and the unloading of a module can be performed in an elegant way too. Further, protection functionalities introduced in previous section can also be applied to save the system from run-time failures of modules.

**High real-time performance**. High real-time performance is required as a dynamic module loading mechanism for hard real-time operating systems like HRP2 kernel. Since loadable modules in our mechanism are developed in a static way and generated as native code, the real-time performance can be easily guaranteed after loaded. Moreover, loading and unloading operations are provided as service calls working under task context and will only lock the CPU for a very few cycles. That is to say, using our mechanism has very little influence on the real-time performance of the whole system.

## 2.4.1 Dynamic Creation Extension

Although HRP2 kernel requires all kernel objects and resources to be allocated statically according its static design, it does provide a kernel extension, called Dynamic CReation

Extension (DCRE), that allows kernel objects to be dynamically created or deleted at run time.

DCRE still follows the static methodology of HRP2 kernel by using the object pool design pattern [113]. The maximum number of each kind of kernel object that can be created must be predefined in configuration files at design time. Objects pools for these kernel objects will be generated at compile time and the resources (e.g. data structures like task control blocks) required by them will be allocated statically. During the startup process of kernel, all kernel objects in pools will be set to the 'not in use' state (or the invalid state). An object can be created by obtaining a 'not in use' object from the pool and initializing it to 'in use' state (or the valid state). When an object created dynamically is no longer needed, it can be deleted and returned to its pool by setting back to the 'not in use' state with necessary clean-up process performed. In this way, kernel objects can be created and deleted without dynamic allocation of memory or other resources.

DCRE is designed in the spirit of minimality principle that it does not depend on any prediction of hardware or application. Consequently, the mechanisms for dynamic memory management are not defined by DCRE. However, dynamic memory management is necessary for dynamically creating tasks whose stacks have different size, address and access permissions which can not be determined and allocated statically. Thus, dealing with dynamic memory management is required for designing dynamic module loading mechanisms based on DCRE.

## 2.4.2 Design of Proposed Mechanism

In this subsection, design of the reference model of our dynamic module loading mechanism is described. Our mechanism mainly consists of three kinds of concepts: loadable modules, containers and the loader. Fig. 2.8 provides an overview of these concepts.

Loadable modules are developed by module developers and can be built as binary files containing information for loading and execution. Containers, whose protection policy, memory layout and resource limit can be configured, are kernel objects used to hold a loadable module. The loader is a system service that is responsible for checking and placing a loadable module into a container, preparing it for execution and unloading it when it is no longer needed. System developers can create and configure containers in the base system and use the loader to load module into specific container dynamically. The reference model of these concepts is explained in following subsections.

|                 |           | Ba       | se Sys  |            |             | Module    | Devel                            | opment |      |  |  |

|-----------------|-----------|----------|---------|------------|-------------|-----------|----------------------------------|--------|------|--|--|

|                 | CTR1      |          | Loader  | ľ          | Module ModA |           |                                  |        |      |  |  |

| Kernel O        | space     |          |         |            | ľ           | Kernel C  | bjects                           | 5      |      |  |  |

|                 | nain DOM  | 11       | dynamic |            |             |           |                                  |        |      |  |  |

|                 |           |          |         | ]          | creation    |           | TASK1 TASK2 SEM1 Memory Segments |        |      |  |  |

| Memory          | Segme     | nt Sp    | ace     |            |             |           |                                  |        |      |  |  |

| Segment         |           | Mer      | nory Ob | ject       |             |           |                                  |        |      |  |  |

| Name            | Addr.     | Size     | Attr.   | Permission |             |           | Name                             | Addr.  | Size |  |  |

| "text"          |           | 1MB      | exec    | DOM1:RX    | load        |           | "text"                           |        | 60KB |  |  |

| "data"          |           | 2MB      |         | DOM1:RW    | load        |           | "data"                           |        | 12KB |  |  |

| "shmem" All :RW |           |          |         |            |             | ļ         |                                  |        |      |  |  |

|                 | •         |          |         | <b>^</b>   |             |           |                                  |        | ŧ    |  |  |

| cor             | ocate sta | atically | 11]     | └-<br>     | configu     | re statio | cally                            |        |      |  |  |

| configu         |           |          | I<br>I  | configu    | ration      | file      |                                  |        |      |  |  |

Fig. 2.8 Proposed Dynamic Loading Mechanism

#### 2.4.2.1 Loadable Module

A loadable module (or just module) is a software component that can be dynamically installed into the existing system to provide extended features such as new services, applications or even device drivers. A module installed can be unloaded in order to free the resources allocated to it such as memory, when the functionality provided by it is no longer required.

Logically, a module is a collection of kernel objects and data. All the kernel objects must be defined in a configuration file of the module at design time. Module developers are not allowed to perform any dynamic creation or deletion of kernel objects during the execution of a module. In this way, the resources required by a module can be statically determined at compile time and will be provided by the loader at load time.

Unlike similar concepts in general-purpose operating systems such as loadable kernel modules (LKM) in Linux [109] or kernel-mode drivers in Windows NT [14], which are running in privileged mode without protection, our modules are supported to work in both privileged mode and non-privileged mode with protection.

In order to achieve high reliability while keeping the simplicity, there are some constraints on the development of modules:

**Kernel objects must belong to the same protection domain**. Access permissions of kernel objects are granted in the granularity of protection domain. A module will be loaded into a container, which is associated with a single protection domain, in the base system for execution. Permissions granted to a module depend on the protection domain of its container. Therefore, all kernel objects in a module must be configured to belong to the same protection domain at design time. The protection domain of a module is usually omitted, in which case the protection domain of container will be used at loading. If the protection domain is specified explicitly, the base system is responsible for choosing a suitable container. It should be noted that the protection domain of a module must not be decided freely by the module developers themselves, which can make any protection domain of a module, verification schemes such as storing digital signatures in the module for checking trusted developers should be introduced at the implementation level of our mechanism. The loader in EV3RT does not support signature verifying since its user applications will only be loaded into the predetermined protection domain (i.e. TDOM\_APP).

**Configurations of memory objects are not allowed**. Implementing dynamic memory management with protection is not required to support our mechanism for the simplicity of porting. All the memory protection information such as page tables will be statically generated at compile time of the base system. Since configuring memory objects may result in changing of the memory protection information, it is not allowed in the development of modules. Instead, we provide an approach, which will be described later in the section of container, to controlling memory protection for a module by putting memory contents into segments with access permissions specified by a container.

**Dynamic creation extension (DCRE) cannot be used**. The main purpose of DCRE is to support developing middlewares such as a dynamic loader, rather than to support developing user applications in a dynamic way. Therefore, DCRE does not provide fine-grained access control on managing objects. That is to say, if a protection domain has the permission to use DCRE, tasks in that domain can create objects belonging to any protection domain including the system domain, which may be used to bypass existing protection policy. Further, the allocation of kernel object pools will introduce configurations of memory objects implicitly, which will violate the second constraint. Hence, while the implementation of our mechanism is based on DCRE, using dynamic creation extension is not supported in the development of modules.

Physically, a module is an object file that contains the module information and multiple segments with code or data. The module information consists of a module configuration table and other implementation-specific or application-specific information. An example of the module configuration table is shown Fig. 2.9. Each entry in the module configuration table corresponds to a configuration entry in the configuration file, which represents a static API call such as CRE\_TSK. An entry in the module configuration table has three members: a static API code, a pointer to the argument of that call and a pointer to store the return value. The loader will create kernel objects according to the static API code and the argument. The return value is used to pass information to the module. For example, in Fig. 2.9, the actual ID of TASK1 is unknown at compile time and will be set by the loader through the return value pointer after the kernel object of TASK1 is created.

The memory contents inside a module are divided into segments. There are at least two segments required to support our mechanism, the text segment and the data segment. The text segment is used to store instructions and read-only data, and the module is not permitted to write to the memory space specified by it. The module information must also be placed into the text segment for safety concerns. Static variables such as global variables and static local variables are contained in the data segment which is writable by the module. Stack areas of tasks are generated as static variables as shown in Fig. 2.9 and hence will be put into the data segment. A module may include other segments, specified by its container, like shared memory segment for finer memory management. Most compilers support to place specific memory contents into a particular segment. For example, the GNU Compiler Collection (GCC) [53] allows user to set the section name for variables in source code and put multiple sections into specified segment in linker script.

```

// Content in the configuration file of a module:

// CRE_TSK(TASK1,{TA_ACT,0,task1,TMIN_TPRI,STACK_SIZE,NULL});

ID _module_id_TASK1 __attribute__((section(".module.text")));

static STK_T _module_ustack_TASK1[COUNT_STK_T(STACK_SIZE)];

/* Structure of information used to create a task */

typedef struct t_ctsk {

. . .

} T_CTSK;

/* Array of configuration information for tasks */

static const T_CTSK _module_ctsk_tab[1] = {