# Studies on Design Automation and Arithmetic Circuit Design for Single-Flux-Quantum Digital Circuits

Koji Obata

## Abstract

Superconductive single-flux-quantum (SFQ) circuit technology attracts attention as a next generation technology of integrated circuits because of its ultra-fast computation speed and low power consumption. In SFQ digital circuits, unlike CMOS digital circuits, a pulse is used as a carrier of information and the representation of the logic values is different from that in CMOS digital circuits. Therefore, design automation algorithms and structure of arithmetic circuits suitable for SFQ digital circuits are different from those for CMOS digital circuits. In addition, design of SFQ circuits has been carried out largely manually. For advancing studies of SFQ digital circuits, design automation algorithms which can design high-performance SFQ circuits are important. Furthermore, studies of circuit structure suitable for SFQ arithmetic circuits are also important for designing high-performance circuits. In this dissertation, several design automation algorithms and design of a multiplier which is one of the most important arithmetic circuits are proposed for SFQ digital circuits.

In Chapter 1, the background and the outline of the dissertation are described.

In Chapter 2, the basis of SFQ circuits and the representation of logic values for SFQ digital circuits are described. There are two methods of representation of the logic values. One is 'dual-rail representation' in which "1" and "0" lines are used and the other is 'synchronous clocking representation' in which synchronizing clocks are used.

In Chapter 3, a new method of logic synthesis for dual-rail SFQ digital circuits are proposed. For representing logic functions, a root-shared binary decision diagram (RSBDD) which is a directed acyclic graph constructed from binary decision diagrams is proposed. In the method, first an RSBDD is constructed from given logic functions, and then the number of nodes in the constructed RSBDD is reduced by variable re-ordering. Finally, a dual-rail SFQ digital circuit is synthesized from the reduced RSBDD. The experimental results on benchmark circuits show that the proposed method synthesizes dual-rail SFQ digital circuits that consist of about 27.1% fewer logic elements than those synthesized by a Transduction-based method on average.

In Chapter 4, an algorithm for clock scheduling of synchronous clocking SFQ digital circuits is proposed. In synchronous clocking SFQ digital circuits, all logic gates are driven by clock pulses. Appropriate clock scheduling makes clock frequency of the circuits higher. Given a clock period, the proposed algorithm determines the arrival time of clock pulses of each gate and the delay that should be inserted. The experimental results on benchmark circuits show that inserted delay elements by the proposed algorithm are 59.0% fewer and the height of clock trees are 40.4% shorter on average than those by a straightforward algorithm. The proposed algorithm can also be used to minimize the clock period, thus obtaining 19.0% shorter clock periods on average.

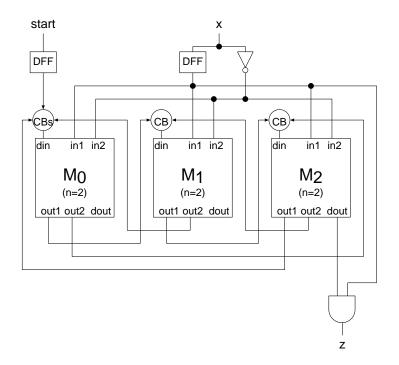

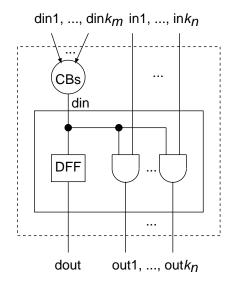

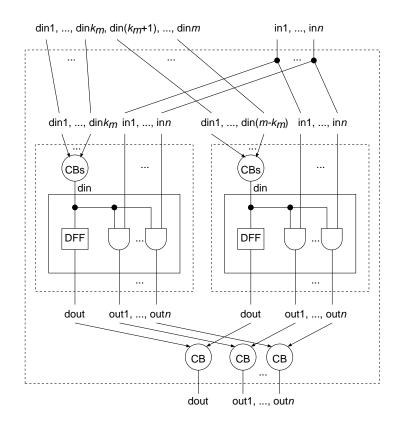

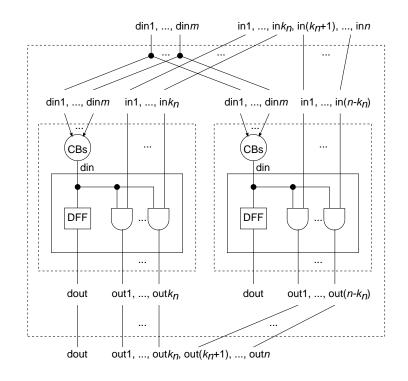

In Chapter 5, a synthesis method of sequential circuits is proposed for synchronous clocking SFQ digital circuits. Since all logic gates of synchronous clocking SFQ digital circuits are driven by a clock signal, synthesis methods of sequential circuits for CMOS digital circuits cannot derive the full power of high-throughput computation of SFQ circuit technology. In the method, a 'state module' consisting of a D flip-flop (DFF) and several AND gates is used. First, states of a sequential machine are encoded by one-hot encoding and state modules are assigned to the states one by one, and then, the modules are connected with each other according to the state transition. For the connection, confluence buffers (CBs), i.e., merger gates without clock signals are used. Consequently, gates driven by a clock signal are removed from its feedback loops, and therefore, a high-throughput SFQ sequential circuit is achieved. The experimental results on benchmark circuits show that compared with a conventional method for CMOS digital circuits, the

proposed method synthesizes circuits that work with 4.9 times higher clock frequency and have 17.3% more gates on average.

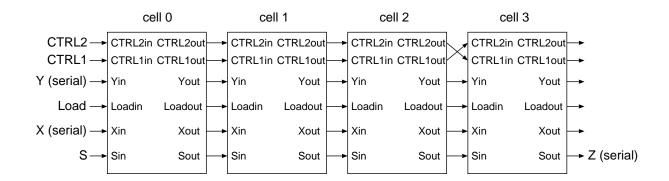

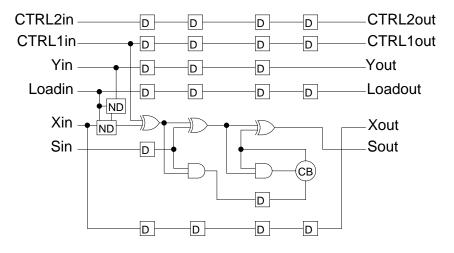

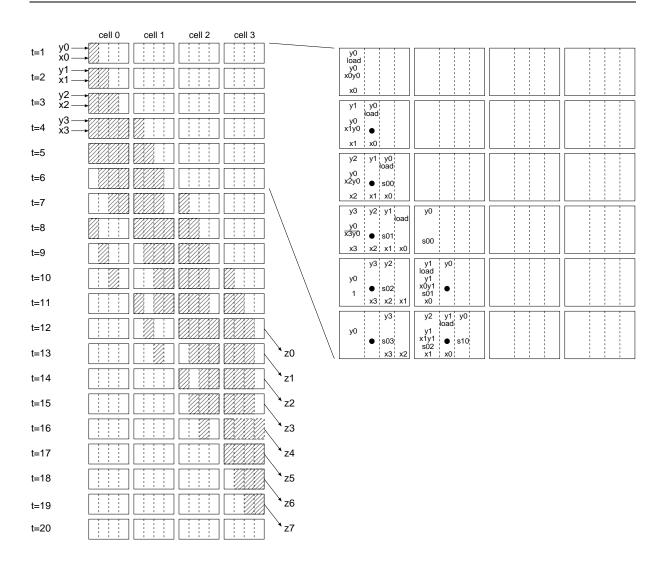

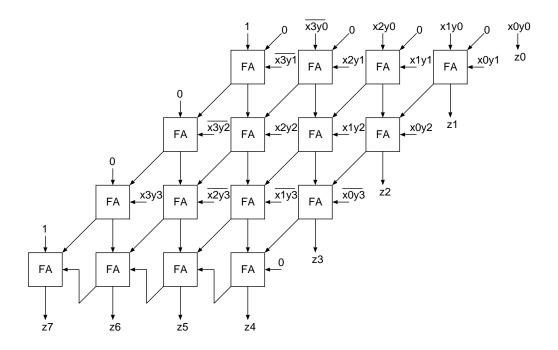

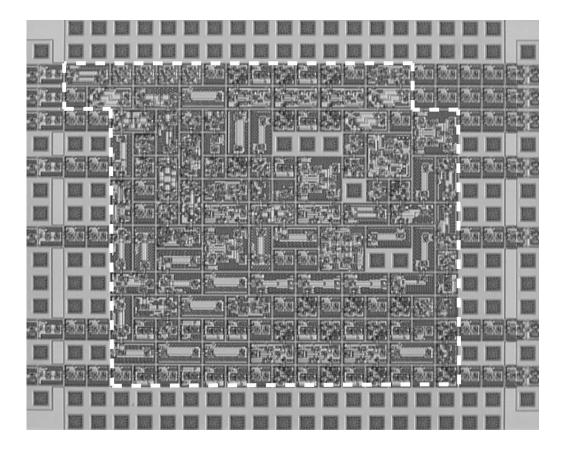

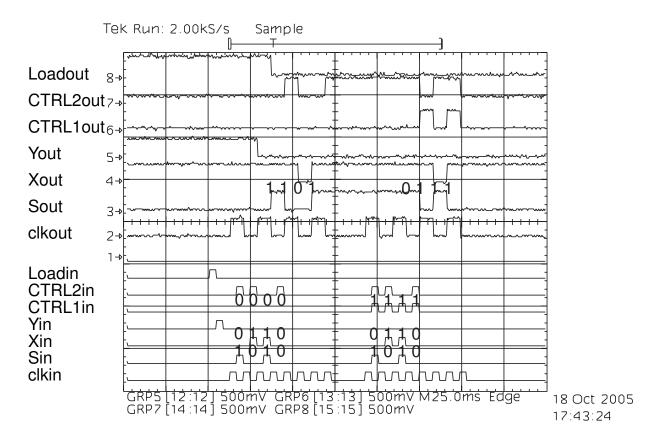

In Chapter 6, an integer multiplier with systolic array structure is proposed for synchronous clocking SFQ digital circuits. The systolic array is a circuit structure for VLSIs and consists of regularly arranged simple processing elements (PEs). For evaluating the proposed multiplier, a 4-bit systolic multiplier and a 4-bit array multiplier which is one of the most typical parallel multipliers are designed and compared with each other. The results of the design and a digital simulation show that the circuit area of the 4-bit systolic multiplier is almost the half of that of the 4-bit array multiplier, and the latency is about 1.5 times longer. Our estimation of the performance of larger scale multipliers shows that the proposed systolic multiplier achieves comparable latency to the array multiplier with extremely smaller circuit area when the bit-width of input is large. A 1-bit PE of the systolic multiplier is fabricated using NEC standard Nb process and successfully tested at low speed.

In Chapter 7, conclusion and future works are stated. The knowledge obtained through the design automation algorithms will be bases of the development of computer-aided design (CAD) systems for SFQ digital circuits. The result obtained through the study of the systolic multiplier is valuable knowledge for designing SFQ arithmetic circuits. Development of SFQ-specific algorithms and methods makes the performance of SFQ digital circuits higher.

## Contents

| A        | ibstract |              |                                                    | i  |  |

|----------|----------|--------------|----------------------------------------------------|----|--|

| 1        | Intr     | Introduction |                                                    |    |  |

|          | 1.1      | Backg        | round                                              | 1  |  |

|          | 1.2      | Outlin       | e of the Dissertation                              | 3  |  |

| <b>2</b> | Pre      | limina       | ries                                               | 7  |  |

|          | 2.1      | Single       | -Flux-Quantum (SFQ) Circuits                       | 7  |  |

|          |          | 2.1.1        | Josephson Junction                                 | 7  |  |

|          |          | 2.1.2        | SFQ Circuits                                       | 8  |  |

|          | 2.2      | Repres       | sentation of Logic Values for SFQ Digital Circuits | 9  |  |

|          |          | 2.2.1        | Dual-Rail Representation                           | 9  |  |

|          |          | 2.2.2        | Synchronous Clocking Representation                | 10 |  |

| 3        | Des      | ign M        | ethod for Dual-Rail SFQ Digital Circuits           | 15 |  |

|          | 3.1      | Introd       | uction                                             | 15 |  |

|          | 3.2      | Dual-I       | Rail SFQ Circuits with $2 \times 2$ -Joins         | 17 |  |

|          |          | 3.2.1        | Dual-Rail SFQ Circuits with $2 \times 2$ -Joins    | 17 |  |

|          |          | 3.2.2        | Resettable $1 \times 2$ -Join                      | 19 |  |

|          | 3.3      | Root-S       | Shared Binary Decision Diagram                     | 20 |  |

|          |          | 3.3.1        | Binary Decision Diagram (BDD)                      | 20 |  |

|          |      | 3.3.2            | Root-Shared Binary Decision Diagram (RSBDD)                            | 21 |

|----------|------|------------------|------------------------------------------------------------------------|----|

|          | 3.4  | Metho            | od of Logic Synthesis                                                  | 23 |

|          |      | 3.4.1            | Flow of Logic Synthesis                                                | 23 |

|          |      | 3.4.2            | Construction of an RSBDD                                               | 24 |

|          |      | 3.4.3            | Reduction of the Size of an RSBDD                                      | 27 |

|          |      | 3.4.4            | Synthesis of a Circuit                                                 | 29 |

|          |      | 3.4.5            | Replacement of $2 \times 2$ -Joins with Resettable $1 \times 2$ -Joins | 34 |

|          | 3.5  | Exper            | imental Results                                                        | 35 |

|          |      | 3.5.1            | Evaluation of Variable Re-ordering techniques                          | 35 |

|          |      | 3.5.2            | Evaluation of the Proposed Method of Logic Synthesis                   | 35 |

|          | 3.6  | Summ             | ary of the Chapter                                                     | 39 |

| 4        | Cla  | alt Sah          | aduling for Supphysical Clashing SEO Digital Circuits                  | 41 |

| 4        |      |                  | eduling for Synchronous Clocking SFQ Digital Circuits                  | 41 |

|          | 4.1  |                  |                                                                        | 41 |

|          | 4.2  |                  | rrent-flow Clocking SFQ Digital Circuits                               | 42 |

|          | 4.3  |                  | Scheduling for Concurrent-flow Clocking SFQ Digital Circuits           | 45 |

|          |      | 4.3.1            | Assumptions for Clock Scheduling                                       | 46 |

|          |      | 4.3.2            | Clock Scheduling Problem                                               | 47 |

|          |      | 4.3.3            | Straightforward Algorithm                                              | 49 |

|          |      | 4.3.4            | Proposed Algorithm                                                     | 51 |

|          |      | 4.3.5            | An Example: Clock Scheduling of a Full Adder                           | 56 |

|          | 4.4  | Evalua           | ation of the Proposed Algorithm                                        | 60 |

|          |      | 4.4.1            | Comparison with an ILP Solver                                          | 60 |

|          |      | 4.4.2            | Comparison with the Straightforward Algorithm                          | 62 |

|          | 4.5  | Summ             | ary of the Chapter                                                     | 63 |

| <b>5</b> | Seq  | uential          | l Circuit Synthesis for Synchronous Clocking SFQ Digital               |    |

|          | Cire | $\mathbf{cuits}$ |                                                                        | 67 |

|          | 5.1  | Introd           | uction                                                                 | 67 |

|          |      |                  |                                                                        |    |

|    | 5.2   | SFQ Sequential Circuits Using Synchronous Clocking Representation       | 68          |

|----|-------|-------------------------------------------------------------------------|-------------|

|    | 5.3   | Method for Synthesizing SFQ Sequential Circuit Using One-hot Encoding . | 69          |

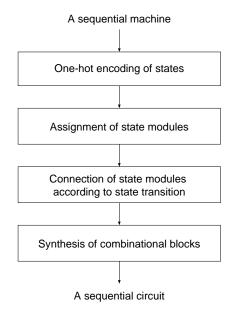

|    |       | 5.3.1 Flow of Sequential Circuit Synthesis                              | 69          |

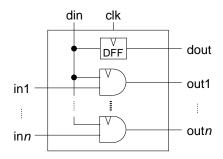

|    |       | 5.3.2 Assignment of State Modules                                       | 70          |

|    |       | 5.3.3 Connection of State Modules                                       | 71          |

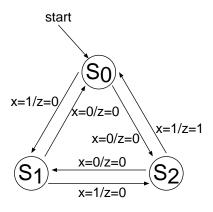

|    |       | 5.3.4 An Example: Synthesis of A Sequential Circuit                     | 72          |

|    |       | 5.3.5 Construction of State Modules                                     | 73          |

|    | 5.4   | Experimental Results                                                    | 76          |

|    | 5.5   | Summary of the Chapter                                                  | 78          |

| 6  | Inte  | eger Multiplier with Systolic Array Structure                           | 81          |

|    | 6.1   | Introduction                                                            | 81          |

|    | 6.2   | Integer Multiplier with Systolic Array Structure                        | 83          |

|    |       | 6.2.1 Systolic Array                                                    | 83          |

|    |       | 6.2.2 Integer Multiplier with Systolic Array Structure                  | 83          |

|    | 6.3   | Design and Evaluation of the Proposed Multiplier                        | 86          |

|    | 6.4   | Test Result of the Proposed Multiplier                                  | 90          |

|    | 6.5   | Summary of the Chapter                                                  | 91          |

| 7  | Con   | clusion                                                                 | 95          |

| A  | cknov | wledgment 1                                                             | L05         |

| Li | st of | Publications by the Author 1                                            | L <b>07</b> |

## List of Figures

| 2.1 | A structure of a Josephson junction.                                                | 7  |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | A general structure of an SFQ circuit                                               | 8  |

| 2.3 | A behavior of an SFQ circuit.                                                       | 8  |

| 2.4 | A representation of logic values and a general circuit structure using dual-        |    |

|     | rail representation.                                                                | 10 |

| 2.5 | A representation of logic values and a general circuit structure using syn-         |    |

|     | chronous clocking representation.                                                   | 11 |

| 2.6 | A circuit structure with zero-skew clocking.                                        | 12 |

| 2.7 | A circuit structure with counter-flow clocking                                      | 12 |

| 2.8 | A circuit structure with concurrent-flow clocking.                                  | 13 |

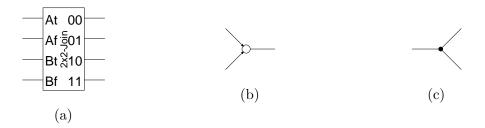

| 3.1 | Notations of basic elements: (a) $2 \times 2$ -Join, (b) CB, (c) SPL                | 17 |

| 3.2 | $2 \times 2$ -Join: (a) JJ schematic, (b) input-output relations                    | 17 |

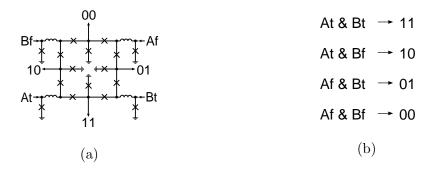

| 3.3 | Two design examples of a full adder using $2 \times 2$ -Joins: (a) the circuit with |    |

|     | the fewest number of $2 \times 2$ -Joins, (b) the circuit consists of AND, OR and   |    |

|     | XOR using $2 \times 2$ -Joins and CBs                                               | 18 |

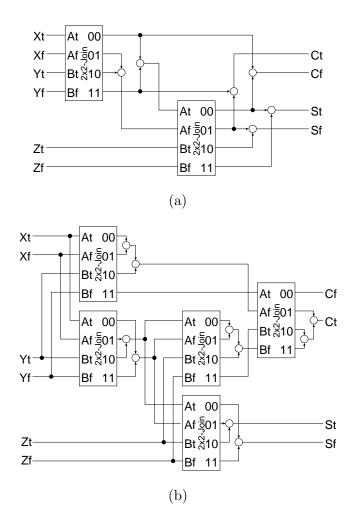

| 3.4 | A 2×2-Join where two of 4 outputs are not used. $\ldots$                            | 19 |

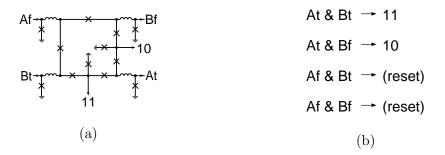

| 3.5 | Resettable 1×2-Join: (a) JJ schematic, (b) input-output relations                   | 19 |

| 3.6 | Notation of a resettable 1×2-Join                                                   | 20 |

| 3.7 | An example of an RSBDD                                                              | 21 |

| 3.8  | Flow of logic synthesis.                                                             | 23       |

|------|--------------------------------------------------------------------------------------|----------|

| 3.9  | Process of constructing RSBDD of the full adder function.                            | 25       |

| 3.10 | Example of level exchange: (a) an original RSBDD, (b) after splitting a              |          |

|      | node and cancellation of sharing functions, (c) after exchange of level $i$ and      |          |

|      | level $i + 1$ , (d) after merging of mergeable pairs                                 | 28       |

| 3.11 | Process of synthesizing a full adder                                                 | 30       |

| 3.12 | Example of replacement with a resettable $1 \times 2$ -Join: (a) before replacement, |          |

|      | (b) after replacement with a resettable $1 \times 2$ -Joins                          | 34       |

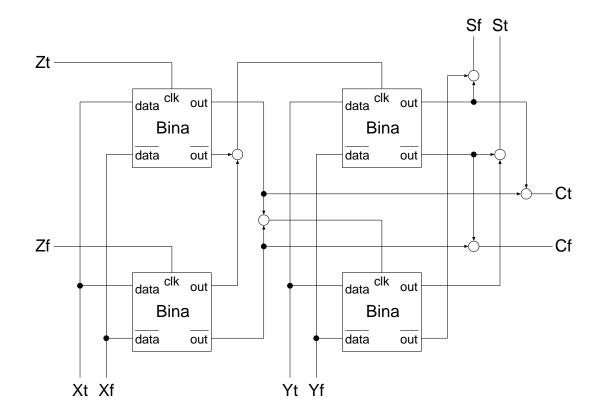

| 3.13 | Bina                                                                                 | 36       |

| 3.14 | A full adder using Binas                                                             | 37       |

| 3.15 | 2x2-AND/XOR                                                                          | 38       |

| 4.1  | An example of a concurrent-flow clocking circuit.                                    | 43       |

| 4.2  | An example of clock scheduling.                                                      | 44       |

| 4.3  | A part of a circuit with the assumptions.                                            | 46       |

| 4.4  | Timing diagram of a gate pair.                                                       | 48       |

| 4.5  | Straightforward algorithm.                                                           |          |

| 4.6  | An illustration of the straightforward algorithm.                                    | 50       |

| 4.7  | Proposed algorithm.                                                                  | 52       |

| 4.8  | Examples requiring Step 3.                                                           | 52<br>53 |

| 4.9  | An example requiring Step 4                                                          | 55<br>54 |

|      |                                                                                      |          |

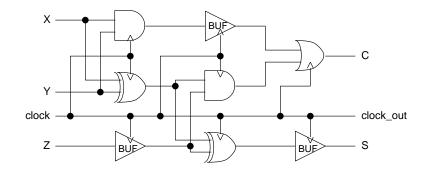

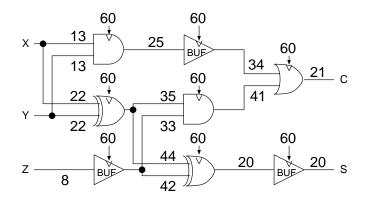

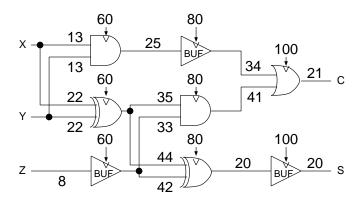

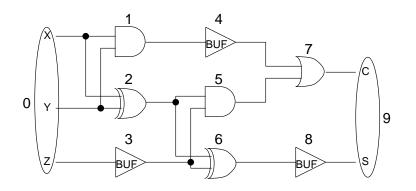

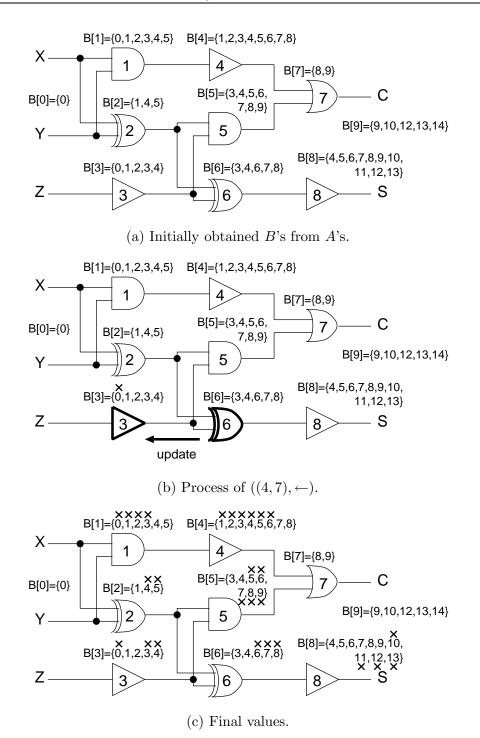

|      | A full adder.                                                                        | 55       |

| 4.11 | Application for a full adder                                                         | 59       |

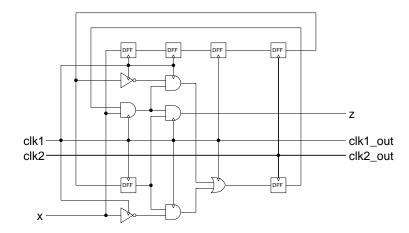

| 5.1  | An example of an SFQ sequential circuit with binary encoding                         | 69       |

| 5.2  | Flow of the sequential circuit synthesis                                             | 70       |

| 5.3  | State module.                                                                        | 71       |

| 5.4  | An example: state transition diagram.                                                | 72       |

| 5.5  | An example: synthesized circuit                                                      | 72       |

| 5.6 | A basic cell                                                                     | 74 |

|-----|----------------------------------------------------------------------------------|----|

| 5.7 | A case of $m = 2k_m$ and $n = k_n$                                               | 75 |

| 5.8 | A case of $m = k_m$ and $n = 2k_n$                                               | 76 |

| 6.1 | 4-bit integer multiplier                                                         | 85 |

| 6.2 | 1-bit cell of the proposed multiplier. (D is a DFF, ND is a non-destructive      |    |

|     | read-out (NDRO) and CB is a confluence buffer.)                                  | 86 |

| 6.3 | Flow of a 4-bit multiplication                                                   | 87 |

| 6.4 | Circuit structure of a 4-bit array integer multiplier                            | 88 |

| 6.5 | Chip photograph of the 1-bit cell. (The number of JJs is $577$ and the circuit   |    |

|     | area is 0.60 mm × 0.56 mm.) $\ldots$                                             | 91 |

| 6.6 | Test result of the 1-bit cell. (The test pattern of the left side is $Y = 1$ ,   |    |

|     | CTRL1 = 0, S = 0101 and $X = 0110$ , and the result is 1011. The test            |    |

|     | pattern of the right side is $Y = 1$ , $CTRL1 = 1$ , $S = 0101$ and $X = 0110$ , |    |

|     | and the result is 1110.) $\ldots$                                                | 92 |

## List of Tables

| 3.1 | Experimental results of variable re-ordering.                                        | 36 |

|-----|--------------------------------------------------------------------------------------|----|

| 3.2 | Experimental results of logic synthesis                                              | 38 |

| 4.1 | The parameters of gates and elements (ps)                                            | 55 |

| 4.2 | A comparison of the proposed algorithm with an ILP solver. $\ldots$ . $\ldots$ .     | 61 |

| 4.3 | Specification of the benchmark circuits                                              | 63 |

| 4.4 | A comparison of the proposed algorithm with the straightforward algorithm.           | 64 |

| 4.5 | The minimum clock periods                                                            | 66 |

| 5.1 | The delay of gates.                                                                  | 76 |

| 5.2 | Experimental results of sequential circuit synthesis (1). $\ldots$ $\ldots$ $\ldots$ | 79 |

| 5.3 | Experimental results of sequential circuit synthesis (2). $\ldots$ $\ldots$ $\ldots$ | 80 |

| 6.1 | The number of JJs and the latency of the designed multiplier. $\ldots$ .             | 89 |

| 6.2 | The estimated number of JJs of larger scale multipliers                              | 90 |

| 6.3 | The estimated latency of larger scale multipliers                                    | 90 |

### Chapter 1

## Introduction

#### 1.1 Background

Recent advances in information and communication technology have been supported by the continuous progress of CMOS integrated circuits. However, the progress faces difficulties because of the limit of miniaturization, the heat dissipation, the increase of interconnect delay and so on. To overcome the difficulties, many technologies have been studied. Superconductive single-flux-quantum (SFQ) circuit technology[1] is one of such technologies. In the report of International Technology Roadmap for Semiconductor (ITRS) published in 2003, SFQ circuit technology was ranked at the highest position for the next generation technology of integrated circuits[2]. Various studies on SFQ circuit technology have been carried out[3–24].

SFQ circuits consist of Josephson junctions (JJs) and inductances. An SFQ pulse which is generated at a JJ is used as a carrier of information. The width of an SFQ pulse is several picoseconds and the height is about 1 mV. Switching energy of a gate of SFQ circuits is much smaller than that of CMOS circuits and switching speed is faster. By using SFQ circuits, ultra-fast computation unachievable by CMOS circuits is expected. Until now, process technologies[4], cell libraries[5,6], processor architectures[7–12], network switches[13], arithmetic circuits[14, 15], interconnection technologies[16–18], cryocooled systems[19] and so on have been studied using tiny prototype circuits. In addition, design of the circuits has been carried out largely by manually placing and routing optimized parts called cells. It is expected that relatively large integrated circuits will be achieved in the near future by the advance of process technology. To design larger scale circuits, computer-aided design (CAD) including design automation is indispensable and studies on design automation algorithms suitable for SFQ circuits are important.

In SFQ digital circuits, pulses are used for representing the logic values "1" and "0." When the presence and the absence of a pulse are simply assigned to the logic values "1" and "0," the logic value "0" and the state of "no signal" is indistinguishable. Therefore, in SFQ digital circuits, two methods are used for representing the logic values[3]. One is 'dual-rail representation' in which "1" and "0" lines are used and the other is 'synchronous clocking representation' in which synchronizing clocks are used. Since these representation methods are different from those of CMOS digital circuits, circuit structure suitable for arithmetic circuits is different.

As interconnections in SFQ digital circuits, Josephson-transmission-lines (JTLs)[1] have been used. JTLs consist of JJs and the transmission delay of unit length is comparable with that of logic gates. Now, transmission lines without JJs are developed as next generation interconnections of SFQ circuits[16–18]. The transmission lines are called passive-transmission-lines (PTLs) and can transmit pulses at almost the speed of light. Since many studies have been carried out on designs using JTLs, the potential of PTLs is not derived.

In this dissertation, we propose design automation algorithms and design of an arithmetic circuit for SFQ digital circuits. Advancement of SFQ circuit technology largely relies on the development of CAD systems which can achieve high-performance (e.g., small-area, high-throughput) circuits and can design circuits systematically. There are many study topics such as logic synthesis, clock scheduling, clock tree synthesis, placement and routing and verification. In addition, studies on circuit structure of arithmetic circuits suitable for SFQ digital circuits are also important for the advancement of SFQ circuit technology because suitable circuit structure of SFQ arithmetic circuits is different from that of CMOS arithmetic circuits. Several studies have been carried out[20, 23, 24].

For design automation algorithms, we focus on logic synthesis and clock scheduling. For dual-rail SFQ digital circuits, we propose a new method of logic synthesis. Although dual-rail representation has some advantages in comparison with synchronous clocking representation, it has not been used because circuit area tends to be larger. It is important to develop a method of logic synthesis which can reduce circuit area. For synchronous clocking SFQ digital circuits with PTLs, we propose an algorithm of clock scheduling. Clock scheduling becomes important when PTLs are used as interconnections because it largely affects the performance of circuits. For synchronous clocking SFQ digital circuits, we propose a synthesis method of sequential circuits. Since all logic gates are driven by clock pulses, conventional synthesis methods of sequential circuit spoil the power of high-throughput computation of an SFQ digital circuit. It is important to develop a new method which can utilize the power. As an SFQ arithmetic circuit, we focus on multiplication and propose a multiplier suitable for SFQ digital circuits because multiplication is one of the most important arithmetic operations.

Using the design automation algorithms to be proposed, we can design high-performance SFQ digital circuits systematically. The knowledge obtained through the studies about design automation algorithms will be bases of the development of CAD systems for SFQ digital circuits. In addition, the result obtained through the study of the multiplier is valuable knowledge to design SFQ arithmetic circuits. Development of SFQ-specific algorithms and methods makes the performance of SFQ digital circuits higher.

#### **1.2** Outline of the Dissertation

In Chapter 2, we describe the basis of SFQ circuits and the representation of logic values for SFQ digital circuits.

In Chapter 3, we propose a method of logic synthesis for dual-rail SFQ digital circuits.

Dual-rail representation has some advantages in comparison with synchronous clocking representation. However, since circuit area using dual-rail representation usually becomes larger, dual-rail representation has not been used. If small-area can be achieved using dualrail representation, adoption of dual-rail representation becomes a promising approach for designing SFQ digital circuits. The experimental results on benchmark circuits show that the proposed method can synthesize dual-rail SFQ digital circuits which consist of about 27.1% fewer logic elements than those synthesized by a Transduction-based method on average.

In Chapter 4, we propose a clock scheduling algorithm for synchronous clocking SFQ digital circuits with PTLs. Clock scheduling becomes important when PTLs are used as interconnections because it largely affects the performance (e.g., clock frequency and/or area) of circuits. Development of good clock scheduling algorithms leads synchronous clocking SFQ digital circuits to high-throughput and small-area circuits. The experimental results on benchmark circuits show that for a given clock period, the proposed algorithm can obtain near optimal solutions in which inserted delay elements are 59.0% fewer and the height of clock trees are 40.4% shorter on average than those by a straightforward algorithm. The minimum clock periods are 19.0% shorter on average than those by the straightforward algorithm.

In Chapter 5, we propose a synthesis method of sequential circuits (circuits with feedback loops) for synchronous clocking SFQ digital circuits. Since all logic gates are driven by clock pulses, conventional synthesis methods of sequential circuits spoil the power of high-throughput computation of an SFQ digital circuit. For achieving high-performance SFQ sequential circuits, it is important to develop a new method which can utilize the power. The experimental results on benchmark circuits show that compared with a conventional method for CMOS digital circuits, the proposed method synthesizes circuits that work with 4.9 times higher clock frequency and have 17.3% more gates on average.

In Chapter 6, we propose an integer multiplier suitable for synchronous clocking SFQ digital circuits based on the systolic array scheme. Since SFQ digital circuits work by

pulse logic, logic gates of SFQ digital circuits have different features from those of CMOS digital circuits. Suitable circuit structure of SFQ arithmetic circuits is different from that of CMOS arithmetic circuits. Therefore, the importance of studies on such suitable circuit structure is increasing. The design of 4-bit multipliers and our estimation of the performance of larger scale multipliers show that the proposed systolic multiplier achieves comparable latency to an array multiplier with extremely smaller circuit area when the bit-width of input is large.

In Chapter 7, we conclude this dissertation and state future works.

### Chapter 2

## Preliminaries

#### 2.1 Single-Flux-Quantum (SFQ) Circuits

#### 2.1.1 Josephson Junction

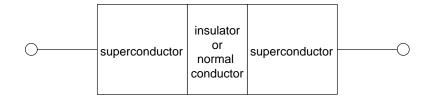

A Josephson junction (JJ) consists of two weakly coupled superconductors which are separated by a very thin insulator or normal conductor as shown in Fig. 2.1. A Josephson junction has the following characteristics called the Josephson effects.

- When a DC current  $I < I_C$  ( $I_C$  is the critical current of the Josephson junction) is applied to the Josephson junction, no voltage is present on the junction though the current flows. This is the DC Josephson effect.

- When a DC current  $I \ge I_C$  is applied, a voltage is present and the junction switches to a finite voltage state. In this case, the phase varies with the voltage that is present

Figure 2.1: A structure of a Josephson junction.

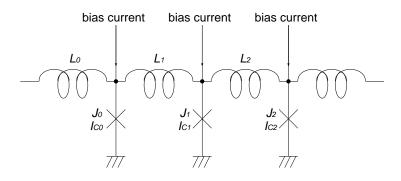

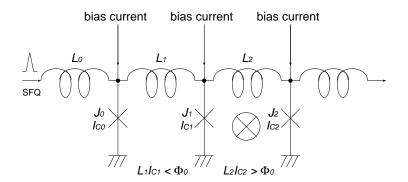

Figure 2.2: A general structure of an SFQ circuit.

Figure 2.3: A behavior of an SFQ circuit.

on the junction and an AC current whose frequency is proportional to the changes of the phase flows. This is the AC Josephson effect.

#### 2.1.2 SFQ Circuits

An SFQ circuit consists of Josephson junctions and inductances as shown in Fig. 2.2. Here, L indicates an inductance of superconductive loops, J indicates a Josephson junction and  $I_C$  indicates the critical current of the Josephson junction. When a Josephson junction of a superconductive loop switches, a flux quantum, i.e., an SFQ,  $\Phi_0$  moves to its adjacent loop. In addition, when the junction switches, a very short voltage pulse V(t) called an SFQ pulse is present. Then,

$$\int V(t)dt = \Phi_0 \simeq 2.07 \quad [mV \times ps]$$

(2.1)

holds.

In SFQ circuits, an SFQ can be stored in the loop or transmitted to its adjacent loop according to the values of L and  $I_C$ . If

$$LI_C < \Phi_0$$

holds, an SFQ is transmitted to its adjacent loop. On the other hand, if

$$LI_C > \Phi_0$$

holds, an SFQ is stored in the loop. When the next SFQ is input, the stored SFQ is transmitted to its adjacent loop. We show a behavior of an SFQ circuit in Fig. 2.3. An SFQ input from the left edge is transmitted from the superconductive loop  $J_0-L_1-J_1$  to  $J_1-L_2-J_2$  because  $L_1I_{C1} < \Phi_0$  holds. In  $J_1-L_2-J_2$ , since  $L_2I_{C2} > \Phi_0$  holds, the SFQ is stored in the loop.

#### 2.2 Representation of Logic Values for SFQ Digital Circuits

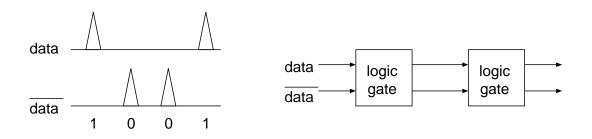

In SFQ digital circuits, SFQ pulses are used for representing the logic values "1" and "0." When the presence and the absence of a pulse are simply assigned to the logic values "1" and "0," the logic value "0" and the state of "no signal" is indistinguishable. Therefore, in SFQ digital circuits, two methods are used for representing the logic values. One is 'dual-rail representation' and the other is 'synchronous clocking representation.'

#### 2.2.1 Dual-Rail Representation

In dual-rail representation, two signal lines are used for representing two logic values "1" and "0." If there is a pulse on the signal line "1," it represents the logic value "1," while if

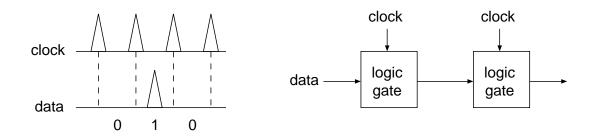

Figure 2.4: A representation of logic values and a general circuit structure using dual-rail representation.

there is a pulse on the signal line "0," it represents the logic value "0." Data can be input with the restriction that the data do not overtake previous data in all paths. Therefore, to achieve high operating frequency, arrangement of the delay of all paths is necessary. Process variation, timing jitters and so on may vary the delay. A circuit using dual-rail representation always works correctly by lowering its operating frequency even if such delay variation occurs. However, since two signal lines are necessary for representing the two logic values "1" and "0" of one signal, the circuit area using dual-rail representation tends to be larger. A representation of logic values and a general circuit structure are shown in Fig. 2.4. A circuit using dual-rail representation is called dual-rail circuits.

#### 2.2.2 Synchronous Clocking Representation

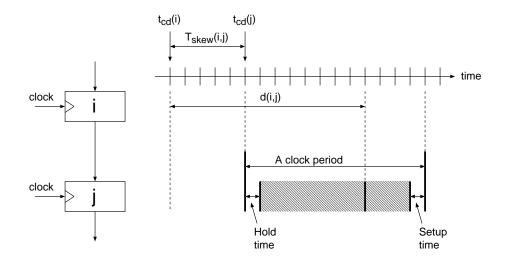

In synchronous clocking representation, synchronizing clocks are introduced in order to represent the logic values. The two logic values, i.e., "1" and "0," are represented by the presence and the absence of a pulse on a data line in a clock period, respectively. A representation of logic values and a general circuit structure are shown in Fig. 2.5. For a gate with clock input (clocked gate), similar to flip-flops (FFs) of CMOS digital circuits, there are constraints between input timing of data and clock signals. One is hold time constraint and the other is setup time constraint. For a clocked gate a, we let  $t_{clk}(a)$  be the time of clock input,  $t_{data}(a)$  be the time of data input,  $\delta_S(a)$  be the setup time,  $\delta_H(a)$

Figure 2.5: A representation of logic values and a general circuit structure using synchronous clocking representation.

be the hold time and  $T_{CP}$  be the clock period. Then, the following inequalities have to hold for working the gate correctly.

$$t_{data}(a) \geq t_{clk}(a) + \delta_H(a) \tag{2.2}$$

$$t_{data}(a) \leq t_{clk}(a) + T_{CP} - \delta_S(a)$$

(2.3)

Ineq. (2.2) is the hold time constraint and indicates that input of data pulses is prohibited for a certain period, i.e.,  $\delta_H(a)$ , after the input of a clock pulse. Ineq. (2.3) is the setup time constraint and indicates that input of data pulses is prohibited for a certain period, i.e.,  $\delta_S(a)$ , before the input of a clock pulse.

In synchronous clocking representation, there are the following four methods of clock supply[3].

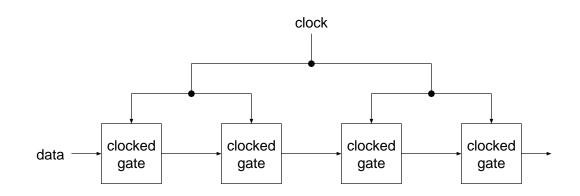

**Zero-skew clocking** A clock signal is provided for all clocked gates simultaneously. This method is widely used in CMOS digital circuits. A circuit structure with zero-skew clocking is shown in Fig. 2.6. We let d(i, j) be the data delay between gates i and j. Then, the minimum clock period  $T_{zero-skew}^{MIN}$  that is achievable using zero-skew clocking is represented by the following equation:

$$T_{zero-skew}^{MIN} = \max_{i,j} \{ d(i,j) + \delta_S(j) \}.$$

Figure 2.6: A circuit structure with zero-skew clocking.

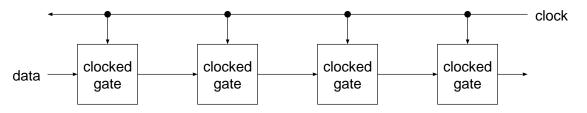

Figure 2.7: A circuit structure with counter-flow clocking.

**Counter-flow clocking** The direction of clock flow is opposite to that of data flow. A clock signal is input from the output side of the circuit. Since the direction is opposite, no collision occurs between the data of present time and that of former time. In addition, violations on the hold time constraint are not likely to occur in comparison with zero-skew clocking. However, it is difficult to achieve high clock frequency. A circuit structure with counter-flow clocking is shown in Fig. 2.7. We let c(i, j) be the clock delay between gates i and j. Then, the minimum clock period  $T_{counter}^{MIN}$  that is achievable using counter-flow clocking is represented by the following equation:

$$T_{counter}^{MIN} = \max_{i,j} \{ c(i,j) + d(i,j) + \delta_S(j) \}.$$

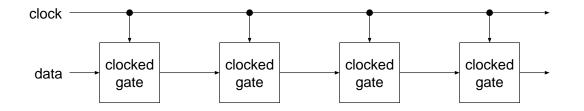

**Concurrent-flow clocking** The direction of clock flow is the same as that of data flow. A clock signal has to arrive at each clocked gate before the arrival of the corresponding data.

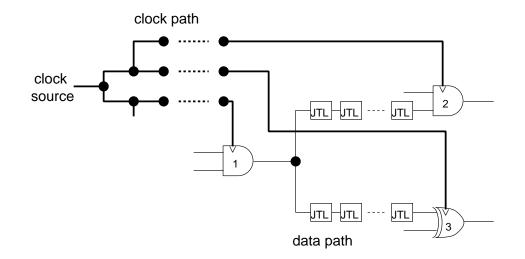

Figure 2.8: A circuit structure with concurrent-flow clocking.

It is possible to make clock frequency high in comparison with zero-skew or counter-flow clocking. However, timing design is difficult. A circuit structure with concurrent-flow clocking is shown in Fig. 2.8. The minimum clock period  $T_{concurrent}^{MIN}$  that is achievable using concurrent-flow clocking is represented by the following equation:

$$T_{concurrent}^{MIN} = \max_{j} \{ \delta_H(j) + \delta_S(j) \}$$

**Clock-follow-data clocking** Similar to concurrent-flow clocking, the direction of clock flow is the same as that of data flow. The different point is that data have to arrive at each clocked gate before the arrival of the corresponding clock signal. One clock pulse carries data from the circuit input to the output. The minimum clock period that is achievable using clock-follow-data clocking is the same as that in concurrent-flow clocking.

Now, concurrent-flow clocking is widely used in SFQ digital circuits because it is possible to make clock frequency high. Malfunction may occur when delays of each path in the circuit vary because of process variation, timing jitters and so on. Therefore, careful timing design is necessary. A circuit using synchronous clocking representation is called synchronous clocking circuits.

### Chapter 3

# Design Method for Dual-Rail SFQ Digital Circuits

#### 3.1 Introduction

In this chapter, we propose a new method of logic synthesis for dual-rail SFQ digital circuits. Dual-rail circuits have some advantages in comparison with synchronous clocking circuits. For example, timing design of dual-rail SFQ digital circuits is easy in comparison with synchronous clocking SFQ digital circuits. This feature is favorable for developing CAD systems. In addition, since dual-rail circuits always works correctly by lowering those operating frequency even if delay variation occurs, the robustness of circuits is higher. However, the circuit area of dual-rail SFQ digital circuits tends to be larger because two signal lines are necessary for representing the two logic values, i.e., "1" and "0," and dual-rail representation has not been used. If small-area circuits can be achieved, adoption of dual-rail representation becomes a promising approach for designing SFQ digital circuits. Therefore, it is important to develop logic elements and design methods which can reduce signal lines and circuit area. As a logic element suitable for this aim, a  $2\times 2$ -Join has been proposed[21, 22]. By using a  $2\times 2$ -Join, some confluence buffers (CBs)[1] and some splitters (SPLs)[1], we can achieve arbitrary logic operations. An SPL is an element which

splits an input pulse to two outputs, while a CB is an elements which merges pulses from two input terminals into one. A  $2\times 2$ -Join is a universal logic element with a small area for dual-rail SFQ digital circuits.

In the new method to be proposed, we use the  $2\times2$ -Join as a logic element. For representation of logic functions, we propose a root-shared binary decision diagram (RSBDD) which is a directed acyclic graph constructed from binary decision diagrams (BDDs)[25, 26]. For reduction of the circuit area, we also propose a new element called resettable  $1\times2$ -Join. In the method of logic synthesis, first we construct an RSBDD from given logic functions, and then reduce the number of nodes in the constructed RSBDD by a variable re-ordering technique. Finally, we synthesize a circuit with  $2\times2$ -Joins and resettable  $1\times2$ -Joins from the reduced RSBDD. For synthesizing larger scale digital circuits, the number of nodes in an RSBDD is an important factor because the number of logic elements included in a synthesized circuit is affected by the number of nodes in the RSBDD. In the variable re-ordering technique, we search for good variable ordering by exchanging nodes in adjacent levels.

For the evaluation of the proposed method, we have implemented the method and have synthesized some benchmark circuits. The experimental results show that the proposed method can synthesize dual-rail SFQ digital circuits which consist of about 27.1% fewer logic elements than those synthesized by a Transduction-based method.

This chapter is organized as follows. In Section 3.2, we describe dual-rail SFQ circuits with  $2\times 2$ -Joins and propose a new logic element, i.e., resettable  $1\times 2$ -Join, for reduction of the circuit area. In Section 3.3, we propose a root-shared binary decision diagrams (RSBDDs) and in Section 3.4, we propose a method of logic synthesis. In Section 3.5, we show experimental results. Finally, in Section 3.6, we give the summary of this chapter.

Figure 3.1: Notations of basic elements: (a)  $2 \times 2$ -Join, (b) CB, (c) SPL.

Figure 3.2:  $2 \times 2$ -Join: (a) JJ schematic, (b) input-output relations.

#### 3.2 Dual-Rail SFQ Circuits with 2×2-Joins

#### 3.2.1 Dual-Rail SFQ Circuits with 2×2-Joins

In dual-rail representation, two signal lines are used for representing a logic signal. If there is a pulse on the signal line "0" ("*false*-line"), it represents the logic value "0," while if there is a pulse on the signal line "1" ("*true*-line"), it represents the logic value "1." We can input data with the restriction that the data do not overtake previous data in all paths. Therefore, we can achieve high operating frequency by arranging the delay time of all paths.

A  $2\times 2$ -Join[21,22] is a logic element for dual-rail SFQ digital circuits. By using a  $2\times 2$ -Join, some confluence buffers (CBs)[1] and some splitters (SPLs)[1], we can achieve arbitrary logic operations. An SPL is an element which splits an input pulse to two outputs, while a CB is an elements which merges pulses from two input terminals into one. Two input pulses for a CB are not allowed to arrive at the same time. In Fig. 3.1,

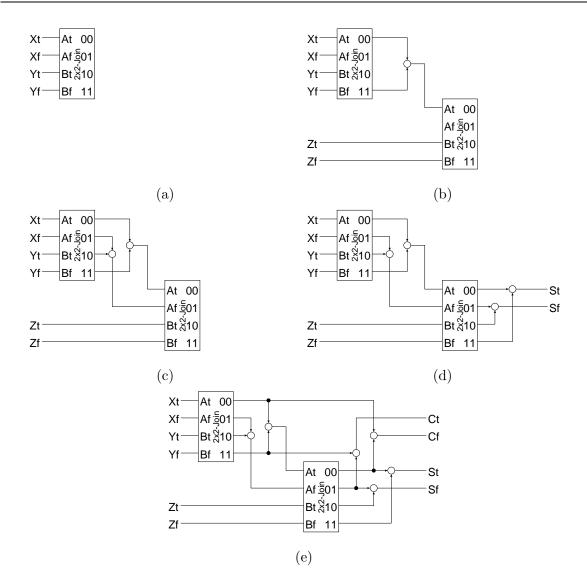

Figure 3.3: Two design examples of a full adder using  $2 \times 2$ -Joins: (a) the circuit with the fewest number of  $2 \times 2$ -Joins, (b) the circuit consists of AND, OR and XOR using  $2 \times 2$ -Joins and CBs.

we show notations of the basic elements that we use in this chapter.

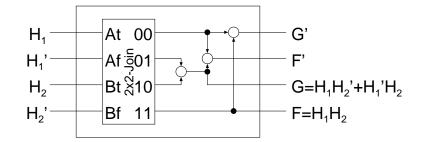

In Fig. 3.2, we show a JJ schematic and input-output relations of a  $2\times 2$ -Join. Each cross in Fig. 3.2 shows a JJ. Dual-rail data are fed into inputs A and B of a  $2\times 2$ -Join, and according to the combination of the input values, a pulse is generated at one of the 4 outputs (00, 01, 10, 11). For example, if pulses are fed into At and Bt, a pulse is generated at output 11. A  $2\times 2$ -Join is a universal logic element with a small area.

As an example of dual-rail SFQ circuits with  $2 \times 2$ -Joins, we show full adders (S =

Figure 3.4: A  $2 \times 2$ -Join where two of 4 outputs are not used.

Figure 3.5: Resettable 1×2-Join: (a) JJ schematic, (b) input-output relations.

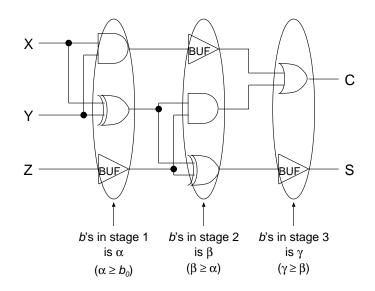

$X \oplus Y \oplus Z$ ,  $C = X \cdot Y + Y \cdot Z + Z \cdot X$ ) in Fig. 3.3. Figure 3.3 (a) shows the circuit with the fewest number of 2×2-Joins. On the other hand, Fig. 3.3 (b) shows the circuit that consists of AND, OR and XOR using 2×2-Joins and CBs. The smallest circuit shown in Fig. 3.3 (a) consists of only two 2×2-Joins, while the circuit shown in Fig. 3.3 (b) consists of 5. By using 2×2-Joins effectively, we can design small-area dual-rail circuits.

#### 3.2.2 Resettable 1×2-Join

In a circuit synthesized with  $2\times 2$ -Joins, CBs and SPLs, there are  $2\times 2$ -Joins whose two of 4 outputs are not used as is shown in Fig. 3.4. For reduction of the circuit area, we propose a new logic element called resettable  $1\times 2$ -Join by removing 2 outputs from a  $2\times 2$ -Join.

A resettable  $1 \times 2$ -Join is a logic element with 4 inputs and 2 outputs. We show a JJ schematic and input-output relations, and a notation of a resettable  $1 \times 2$ -Join in Fig. 3.5 and Fig. 3.6, respectively. A resettable  $1 \times 2$ -Join consists of only 12 JJs in comparison with 16 JJs of a  $2 \times 2$ -Join. When pulses are fed into At and Bt, a pulse is generated

Figure 3.6: Notation of a resettable  $1 \times 2$ -Join.

at output 11 and when pulses are fed into At and Bf, a pulse is generated at output 10. Different from a  $2 \times 2$ -Join, when pulses are fed into Af and Bf/Bt of a resettable  $1 \times 2$ -Join, no pulse is generated and the resettable  $1 \times 2$ -Join is reset.

We have confirmed that a  $2 \times 2$ -Join and a resettable  $1 \times 2$ -Join have almost the same physical characteristics (delay time, operation margins and so on) by an analog circuit simulation.

#### 3.3 Root-Shared Binary Decision Diagram

#### 3.3.1 Binary Decision Diagram (BDD)

A binary decision diagram (BDD) on a variable set  $X = \{x_1, \ldots, x_v\}$  is a directed acyclic graph and represents a logic function  $f : \{0, 1\}^v \to \{0, 1\}$ . As nodes, there are nonterminal nodes labeled by variable  $x_i$  and terminal nodes labeled by the constant "0" or "1." The non-terminal nodes are called variable nodes and the terminal nodes are called leaves. Among variable nodes, there is a root node whose indegree is zero. The outdegree of a variable node is two, while that of a leaf is zero. Each of the two outgoing edges of a variable node has a label. An edge labeled by "0" is called 0-edge and one labeled by "1" is called 1-edge. For an input values of the logic function  $a = (a_1, \ldots, a_v) \in \{0, 1\}^v$ , we can trace the BDD from the root node in accordance with the values of the input. From a node labeled by  $x_i$ , we trace the 0-edge of the node when  $a_i = 0$ , while we trace the 1-edge when  $a_i = 1$ . The value of the leaf that we reach is the value of the logic function with the input values. The BDD can be constructed by applying Shannon expansion to

Figure 3.7: An example of an RSBDD.

the logic function.

We can represent a logic function uniquely using a BDD when variable ordering is fixed, redundant nodes are removed and equivalent nodes are merged. A redundant node is a node whose 0-edge and 1-edge point to the same node. Two nodes are equivalent when they have the same label, the 0-edges of them point to the same node and the 1-edges of them point to the same node. Such BDD is called reduced ordered BDD (ROBDD)[26]. BDDs are widely used in electronic design automation (EDA) fields.

#### 3.3.2 Root-Shared Binary Decision Diagram (RSBDD)

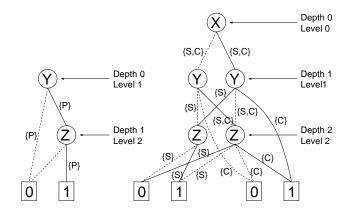

An RSBDD on a variable set  $X = \{x_1, \ldots, x_v\}$  is a directed acyclic graph and represents a set of logic functions  $F = \{f_1, \ldots, f_m\}$   $(f_i : \{0, 1\}^{v_i} \to \{0, 1\}, v_i \leq v)$ . As nodes, there are variable nodes and leaves. Among variable nodes, there are root nodes. Each edge has two labels F'  $(F' \subseteq F)$  and c  $(c \in \{0, 1\})$ . We call the former label 'f-label' and the latter 'c-label.' For a function  $f_i$  and an input values  $a = (a_1, \ldots, a_v) \in \{0, 1\}^v$ , we can trace the RSBDD from one of the root nodes. We trace the edges whose f-labels contain  $f_i$ . From a node labeled by  $x_i$ , we trace the 0-edge of the node when  $a_i = 0$ , while we trace the 1-edge when  $a_i = 1$ . The value of the leaf that we reach is the value of  $f_i$  with the input values. We show an example of an RSBDD in Fig. 3.7. The RSBDD represents functions  $S(X,Y,Z) = X \oplus Y \oplus Z$ ,  $C(X,Y,Z) = X \cdot Y + Y \cdot Z + Z \cdot X$  and  $P(Y,Z) = Y \cdot Z$ . In Fig. 3.7, dashed edges show that c-labels of the edges are 0 and solid edges show that c-labels are 1. " $\{S,C\}$ ," " $\{S\}$ ," " $\{C\}$ " and " $\{P\}$ " are f-labels. The RSBDD consists of two connected parts. The left side part represents  $\{P\}$  and the right side part represents  $\{S,C\}$ .

An RSBDD is constructed by the following rule from BDDs. Variable ordering of all the BDDs is identical. For given variable ordering, if labels of root nodes of the BDDs are not unique, a disconnected graph is constructed.

#### [The rule for constructing an RSBDD of a set of functions F]

- If the size of F is one, the RSBDD of F is obtained by adding f-labels to the BDD representing the function.

- For  $F = F_1 \cup F_2$ , the RSBDD of F is obtained by merging nodes and edges of the RSBDDs of  $F_1$  and  $F_2$  that satisfy the followings.

- Node  $u_1$  of the RSBDD of  $F_1$  and node  $u_2$  of the RSBDD of  $F_2$  are mergeable when their labels are identical and either of the following conditions holds.

- 1. They are root nodes, or

- 2. There is one-to-one relation between the sets of parent nodes of nodes  $u_1$ and  $u_2$  and, all the corresponding parent nodes are mergeable and the clabels of the outgoing edges from the related parent nodes to nodes  $u_1$  and  $u_2$  are identical.

- Edges  $e_1$  and  $e_2$  are mergeable when their start nodes are identical, their end nodes are identical and their c-labels are identical.  $e_1$  and  $e_2$  are to be merged by taking the union of their f-labels.

We define the depth of a root node as 0 and the depth of a variable node except root nodes as the largest depth of its parent nodes plus 1 and the level of a node as the position

Figure 3.8: Flow of logic synthesis.

of the variable of the node in the variable ordering. In the right side part of Fig. 3.7, the depths of the nodes labeled by X, Y and Z are 0, 1 and 2, respectively and in the left side part, the depths of the nodes labeled by Y and Z are 0 and 1, respectively. The levels of the nodes labeled by X, Y and Z are 0, 1 and 2, respectively. We define the size of an RSBDD as the total number of variable nodes and also define the width of a level as the number of nodes in the level. In Fig. 3.7, the size is 7 and the width of level 0, 1 and 2 are 1, 3 and 3, respectively.

## **3.4** Method of Logic Synthesis

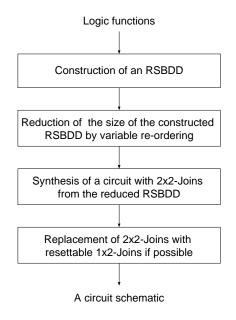

#### 3.4.1 Flow of Logic Synthesis

Now, we propose a method of logic synthesis. We show the flow of the proposed method in Fig. 3.8. We first construct an RSBDD from given logic functions, and then reduce the size of the constructed RSBDD by a variable re-ordering technique. We synthesize a circuit that uses only  $2 \times 2$ -Joins, CBs and SPLs from the reduced RSBDD. Finally, we replace  $2 \times 2$ -Joins with resettable  $1 \times 2$ -Joins if possible for reduction of the circuit area.

Variable ordering of an RSBDD is important because the number of nodes in the RSBDD is affected by the variable ordering of it. Exact minimization of an RSBDD is almost impossible because the computation cost of exact minimization is very high. Therefore, we apply the variable re-ordering technique in [27] to an RSBDD to reduce its size.

#### 3.4.2 Construction of an RSBDD

#### Method of RSBDD Construction

When functions are given by logic expressions, we can construct an RSBDD according to the given functions incrementally.

First, we select one logic function and construct the RSBDD representing the function. Then, we select unprocessed functions one by one and construct the RSBDD from the selected function. If there is a node which is newly created or one whose number of parent nodes varies or one whose parent nodes are merged with other nodes, we check whether mergeable pairs exist and merge all mergeable pairs.

#### Example of RSBDD Construction

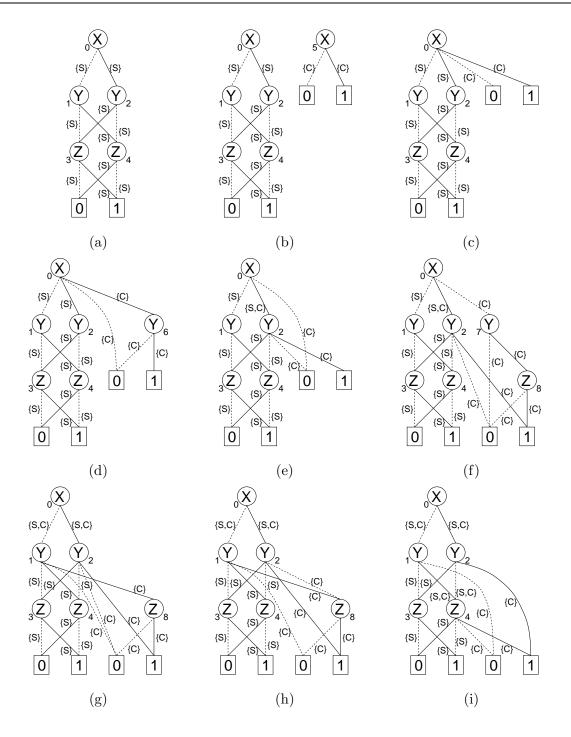

As an example of RSBDD construction, we show the process of constructing an RSBDD of the full adder function  $S(X, Y, Z) = X \oplus Y \oplus Z$  and  $C(X, Y, Z) = X \cdot Y + Y \cdot Z + Z \cdot X$  in Fig. 3.9. We assume the variable ordering is X-Y-Z. In Fig. 3.9, for explanation, we numbered the nodes. We process the functions sequentially.

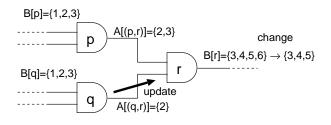

First, we construct the BDD of function S and label all edges of the BDD " $\{S\}$ " as f-labels. Figure 3.9 (a) is the RSBDD of  $\{S\}$ . Then, we process function  $C = X \cdot Y + Y \cdot Z + Z \cdot X$ . Figure 3.9 (b) shows an intermediate step of processing X. Here, nodes 0 and 5 are root nodes and labels of these two nodes are identical. Therefore, we can merge these two nodes. By merging them, we can obtain the RSBDD shown in Fig. 3.9 (c). We

Figure 3.9: Process of constructing RSBDD of the full adder function.

have shown Fig. 3.9 (b) for explanation, although the RSBDD shown in Fig. 3.9 (b) is not constructed actually and the RSBDD shown in Fig. 3.9 (c) is directly constructed from

Fig. 3.9 (a).

Figure 3.9 (d) shows an intermediate step of processing  $X \cdot Y$ . Nodes 2 and 6 have the same label. Furthermore, c-labels of the edges between these two nodes and node 0, that is their parent node, are both 1. Therefore, nodes 2 and 6 are mergeable. By merging them, we can obtain the RSBDD shown in Fig. 3.9 (e).

Figure 3.9 (f) shows an intermediate step of processing  $X \cdot Y + Y \cdot Z$ . In this step, we can merge nodes 1 and 7, and can obtain the RSBDD shown in Fig. 3.9 (g).

Figure 3.9 (h) shows an intermediate step of processing  $X \cdot Y + Y \cdot Z + Z \cdot X$ . In this step, nodes 4 and 8 are mergeable. Their labels are the same, i.e., Z, and c-labels of the edges between these two nodes and node 1 which is one of the parent nodes are the same, i.e., 1, and the edges between these two nodes and node 2 are the same, i.e., 0. By merging these two nodes, we can obtain the RSBDD shown in Fig. 3.9 (i). Similar to Fig. 3.9 (b), the RSBDDs shown in Fig. 3.9 (d), (f) and (h) are not constructed, but the RSBDDs shown in Fig. 3.9 (e), (g) and (i) are directly constructed.

#### Computational Complexity of RSBDD Construction

Now, we consider the computational complexity of constructing an RSBDD. When we check whether two nodes are mergeable, we have to check all parent nodes of the two nodes. The number of parent nodes of a node is the indegree of it. The summation of the number of parent nodes of the nodes in an RSBDD is the summation of their indegrees, which is the number of edges in the RSBDD. For a connected part of the RSBDD, a node is checked at most for all nodes in the same level of the part. Therefore, the computational complexity of constructing an RSBDD is  $O(f \cdot e \cdot w_{\text{max}})$  where f is the number of given logic functions, e is the number of edges in the RSBDD, and  $w_{\text{max}}$  is the maximum width of the connected part of the RSBDD. The computational complexity is  $O(fe^2)$ .

#### 3.4.3 Reduction of the Size of an RSBDD

#### Method of Size Reduction

By searching for good variable ordering and changing variable ordering, we can reduce the size of an RSBDD. The number of root nodes in an RSBDD may vary when variable ordering of it changes. In the proposed method of logic synthesis, we apply the variable re-ordering technique in [27], that is originally proposed for conventional BDDs, to the RSBDD constructed in Section 3.4.2 and reduce the size. We exchange all nodes in adjacent levels by level exchange. We determine strategies of level exchange and reduce the size of the RSBDD.

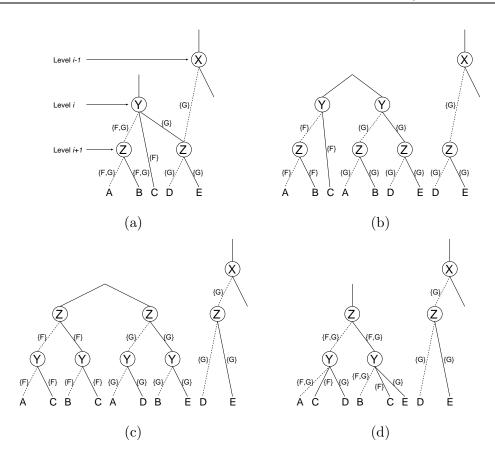

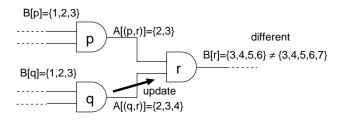

When nodes in adjacent levels are exchanged, all the nodes have to be shared by the same set of functions. If the nodes are shared by a different set of functions, we cancel the sharing. Furthermore, if we exchange nodes in levels i and i + 1, we have to split nodes in level i + 1 whose parent nodes are in levels lower than i. After these processes are carried out, the nodes in level i and those in level i + 1 can be exchanged. After exchange of the nodes, we check whether mergeable pairs exist and if such pairs exist, merge them pairwise.

#### Example of Size Reduction

As an example, we show the level exchange of an RSBDD in Fig. 3.10. Figure 3.10 (a) shows the original RSBDD. We exchange the nodes in level i and those in level i + 1, that is, the nodes labeled by Y and those labeled by Z. First, we cancel the sharing of functions F and G because the right node in level i + 1 is not shared by F and G. Furthermore, since a parent node of the right node in level i + 1 is in level i - 1, we split the right node. We show the RSBDD after the cancellation and the splitting in Fig. 3.10 (b). Then, we exchange the nodes in level i and those in level i + 1. Figure 3.10 (c) shows the RSBDD after the exchange. Finally, we check whether mergeable pairs exist and merge all mergeable pairs. Figure 3.10 (d) shows the RSBDD after the merging.

Figure 3.10: Example of level exchange: (a) an original RSBDD, (b) after splitting a node and cancellation of sharing functions, (c) after exchange of level i and level i + 1, (d) after merging of mergeable pairs.

As a strategy of level exchange, we adopt sifting[27]. We briefly describe sifting here. We assume that variables of a BDD are  $(x_1, \ldots, x_i, \ldots, x_v)$ . When we fix variable ordering except  $x_i$ , we can insert  $x_i$  into v different positions. We search for the position that the size of the BDD is the minimum and move the variable to the position. We select all variables one by one and reduce the size.

#### **Computational Complexity of Size Reduction**

Here, we consider the computational complexity of the level exchange for a connected part of an RSBDD and sifting. First, we consider the computational complexity of the level exchange of level i and level i + 1. We assume the width of level i in an original RSBDD to be  $w_i$ , the width of level i + 1 to be  $w_{i+1}$  and the number of variables to be v. The computational complexity of splitting nodes is  $O(p_{i+1})$  where  $p_{i+1}$  is the number of parent nodes of nodes in level i + 1, and the computational complexity of exchanging nodes is  $O(f \cdot (w_i + w_{i+1}))$ . The computational complexity of the cancellation of sharing functions is  $O(f \sum_{x=i}^{v} n_x)$  where  $n_i$  is the number of nodes in level i. The computational complexity of the merging is  $O(f \cdot w_{\max} \sum_{x=i}^{v} e_x)$  where  $e_i$  is the number of edges in level i. Therefore, the computational complexity of level exchange of level i and i + 1 is  $O(f \cdot w_{\max} \sum_{x=i}^{v} e_x)$ . The computational complexity is  $O(fe^2)$ .

In sifting, selection of variables are carried out v times. The number of level exchange for each selection is 3(v - 1) in the worst case. Therefore, in the worst case, the number of level exchange is 3v(v - 1).

#### 3.4.4 Synthesis of a Circuit

#### Method of Circuit Synthesis

We synthesize a circuit from the RSBDD constructed up to Section 3.4.3. We select connected parts from the RSBDD one by one and synthesize the circuit. Here, we describe a method for synthesizing a circuit block from a connected part of the RSBDD. We describe an example of circuit synthesis later using Fig. 3.11.

We process sequentially from the root node to the leaves. We construct the first stage of the block from the root node and the nodes of depth 1 using 2×2-Joins. Then, we construct the *i*-th ( $i \ge 2$ ) stage from the nodes of depth *i*. Finally, we derive circuit outputs from the leaves.

To select an appropriate signal from the 4 outputs of a  $2\times 2$ -Join, we label a number '0' or '1' to nodes of the RSBDD. We call the number 'output-selection-number.' When the output-selection-number is 0, we select output 00 or 01 of the corresponding  $2\times 2$ -Join

Figure 3.11: Process of synthesizing a full adder.

according to the c-label of the edge of the corresponding node. For example if the c-label of the edge is 0, we select 00. Similarly, when the output-selection-number is 1, we select output 10 or 11.

We construct the first stage from the root node and the nodes of depth 1. For nodes of depth 1 that have the same label, we place a  $2\times 2$ -Join. We connect the *true*-line of the root variable to input At of the  $2\times 2$ -Join, the *false*-line of the root variable to Af, the *true*-line of the variable of depth 1 to Bt and the *false*-line of the variable of depth 1 to

Bf. We mark the root node and the processed nodes of depth 1 with "processed." We let the output-selection-number of the node of depth 1 be 0 or 1 according to the edge of the root node that points to the node being 0 or 1, respectively.

We construct the *i*-th  $(i \ge 2)$  stage from the nodes of depth *i*. For a node of depth *i*, we place a 2×2-Join and connect the *true*-line and the *false*-line of the variable of depth *i* to input Bt and Bf of the 2×2-Join, respectively. We connect intermediate circuit outputs that are constructed up to the previous stages to input At and Af as follows.

To input At, we connect lines that correspond to edges pointing to the processing node. We merge these lines to one line using CBs and connect it to At. When a parent node of the processing node is the root node, we select the *false*-line or the *true*-line of the root variable according to the edge between the parent node and the processing node being a 0-edge or a 1-edge, respectively. When the parent node of the processing node is not the root node, we select an output of the  $2\times 2$ -Join that corresponds to the parent node according to the output-selection-number and the c-label of the edge. From the 4 outputs (00, 01, 10, 11), we select an output whose label is identical to the concatenation of the output-selection-number and the c-label of the edge.

To input Af, we connect lines corresponding to edges that are outgoing from nodes included in paths from the root node to the processing node and are not included in the paths. Selection of lines is carried out in the same way as the case of At. We check whether there are edges that point to an unprocessed node of the same level and that are identical to the edges selected for connecting to Af. If such edges exist, we set the output-selection-number of the unprocessed node to 0 and mark the unprocessed node with "processed." When such an unprocessed node exists, a  $2\times 2$ -Join is shared by two nodes.

We set the output-selection-number of the processing node to 1 and mark the node with "processed." We apply these processes to all unprocessed nodes.

We derive circuit outputs from the leaves of the connected part of the RSBDD. The *false*-lines are derived from 0-leaves and the *true*-lines are derived from 1-leaves. We select

lines in the same way as the case of At.

The number of stages of  $2\times 2$ -Joins in the synthesized circuit block is the maximum depth of the connected part of the RSBDD and the number of  $2\times 2$ -Joins is less than or equal to the number of nodes except the root node. In the best case, the number of  $2\times 2$ -Joins is half of the number of nodes in the connected part of the RSBDD.

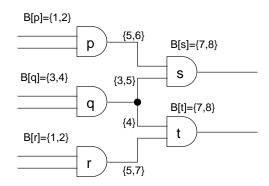

#### **Example of Circuit Synthesis**

As an example of circuit synthesis, we consider a full adder. The RSBDD of a full adder is shown in Fig. 3.9 (i). It consists of one connected part. We show process of the synthesis in Fig. 3.11.

First, we construct the 2×2-Join of the first stage from the root node and the two nodes of depth 1. We prepare one 2×2-Join and connect the *true*-line (Xt) and the *false*line (Xf) of the root variable to input At and Af, respectively and, the *true*-line (Yt) and the *false*-line (Yf) of the variable of depth 1 to Bt and Bf, respectively. We mark the root node and the two nodes of depth 1 with "processed." We set the output-selection-number of node 1 and node 2 to "0" and "1," respectively. We show the circuit that is synthesized up to this step in Fig. 3.11 (a).

Then, we construct the 2×2-Joins of the second stage from nodes of depth 2. Here, we process left side node (node 3) first. We prepare a new 2×2-Join and connect the *true*-line (Zt) and the *false*-line (Zf) of the variable of depth 2 to input Bt and Bf, respectively. We mark the node with "processed" and set the output-selection-number to "1."

To input At, we connect lines that correspond to edges pointing to the node (0-edge of node 1 and 1-edge of node 2). Since the output-selection-number of node 1 is 0 and the output-selection-number of node 2 is 1, output 00 and 11 of the  $2\times 2$ -Join of the first stage are the corresponding lines. We merge these two lines to one line using a CB and connect the merged line to At. The circuit shown in Fig. 3.11 (b) is synthesized up to this step.

To input Af, we connect lines corresponding to edges that are outgoing from nodes

included in the paths from the root node to the processing node and are not included in the paths (1-edge of node 1 and 0-edge of node 2). Therefore, we connect output 01 and 10 of the  $2\times 2$ -Join of the first stage to Af. These lines are identical to lines corresponding to edges pointing to node 4. We set the output-selection-number of node 4 to "0" and mark node 4 with "processed." We complete processing of the nodes of depth 2. The circuit shown in Fig. 3.11 (c) is synthesized up to this step. In this example, we can construct the second stage by using only one  $2\times 2$ -Join.

We derive circuit outputs from the leaves. By constructing circuit outputs of function S (St, Sf), we can synthesize the circuit shown in Fig. 3.11 (d). We also derive circuit outputs of function C (Cf, Ct) and can synthesize a full adder shown in Fig. 3.11 (e).

The number of  $2 \times 2$ -Joins in the full adder is 2 and the number of stages of  $2 \times 2$ -Joins is 2 because the maximum depth of the RSBDD is 2.

#### **Computational Complexity of Circuit Synthesis**

First, we consider the computational complexity of synthesizing a circuit block from a connected part of an RSBDD. When we search for signal lines that are connected to Af, we have to check all ancestor nodes of the processing node. However, by preserving all intermediate results, that is, edges that are included in the paths from the root node to the processing node and edges that are not in the paths, we can search for the signal lines by only checking the parent nodes of the processing node. The number of edges that are preserved in the processing node is less than or equal to the number of all edges in the connected part. Therefore, the computational complexity of searching for the signal lines that are connected to Af is  $O(e_{\text{connected-part}} \cdot q_a)$  where  $e_{\text{connected-part}}$  is the number of edges in the summation of the number of all parent nodes that are included in a connected part is identical to the number of edges in the connected part. Therefore, all parent nodes that are included in a connected part is identical to the number of all parent nodes that are included in a connected part is identical to the number of edges in the connected part. Therefore, the computational complexity of searching for all signals is  $O(e_{\text{connected-part}}^2)$ , and this is the computational complexity of searching for all signals is  $O(e_{\text{connected-part}}^2)$ .

Figure 3.12: Example of replacement with a resettable  $1 \times 2$ -Join: (a) before replacement, (b) after replacement with a resettable  $1 \times 2$ -Joins.

When we synthesize a circuit from an RSBDD, the computational complexity is proportional to the summation of the computational complexity of synthesizing each circuit block, i.e.,  $O(\sum_{c=1}^{g} e_{\text{connected-part } c}^2)$  where g is the number of connected parts of the RSBDD. The computational complexity is  $O(e^2)$ .

#### 3.4.5 Replacement of 2×2-Joins with Resettable 1×2-Joins

In a circuit synthesized up to Section 3.4.4, there can be  $2\times 2$ -Joins where two of the 4 outputs are not used, as shown in Fig. 3.4. By replacing such  $2\times 2$ -Joins with resettable  $1\times 2$ -Joins, we can reduce the circuit area. Since a resettable  $1\times 2$ -Join has almost the same physical characteristics as a  $2\times 2$ -Join, we can reduce the circuit area by simply replacing

the  $2 \times 2$ -Joins shown in Fig. 3.4 with resettable  $1 \times 2$ -Joins. We show an example of the replacement in Fig. 3.12.

### 3.5 Experimental Results

#### 3.5.1 Evaluation of Variable Re-ordering techniques

For evaluating the employed method of variable re-ordering, we have implemented the method by programming language C. In the program, we construct an RSBDD from given logic functions and reduce the size by level exchange with sifting. We show the experimental results on some benchmark circuits of LGSynth'91[28] in Table 3.1. For comparison of the method, we have also implemented other strategies "random" and "window permutation[27]." In the random and window permutation, we have selected a level at random 1,000 times. In addition, we set window size as 3 in the window permutation. The experimental environment is a SunBlade2000 with UltraSPARC-III+ 1.2 GHz CPU and 2 GByte memory.

The experimental results show that sifting is the best among the three strategies. Execution time of the sifting is short in comparison with other strategies and in many cases, the size of the RSBDDs with sifting is the best.

#### 3.5.2 Evaluation of the Proposed Method of Logic Synthesis

For evaluating the proposed method of logic synthesis, we have implemented the method by programming language C. We have synthesized some benchmark circuits in LGSynth'91 benchmark set[28]. In the program, we construct an RSBDD from given logic functions first. Then, we reduce the size of the constructed RSBDD by level exchange with sifting and synthesize a circuit using the reduced RSBDD. In the program, since the number of logic elements does not vary, we have used only  $2 \times 2$ -Joins as logic elements.

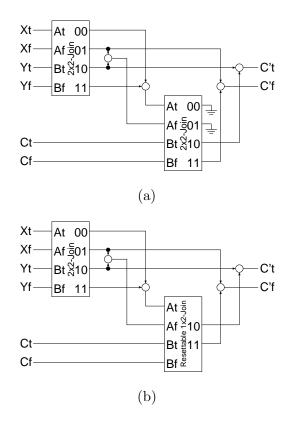

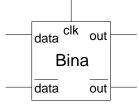

In [20], a BDD-based design method was proposed as another design method of dualrail SFQ circuits. In the design method, a binary switch called Bina[20] is used as a logic

| ,                    | u c    |         |         | sifting |          | random |          | window      |          |

|----------------------|--------|---------|---------|---------|----------|--------|----------|-------------|----------|

| circuit              | # of   | # of    | initial |         |          |        |          | permutation |          |

| name                 | inputs | outputs | size    | size    | CPU      | size   | CPU      | size        | CPU      |

|                      |        |         |         |         | time (s) |        | time (s) |             | time (s) |

| alu2                 | 10     | 6       | 200     | 150     | 9.9      | 139    | 40.1     | 158         | 160.5    |

| alu4                 | 14     | 8       | 1363    | 355     | 105.9    | 1151   | 449.9    | 535         | 475.7    |

| $\operatorname{cmb}$ | 16     | 4       | 35      | 27      | 6.9      | 27     | 18.4     | 35          | 110.4    |

| f51m                 | 8      | 8       | 35      | 35      | 3.9      | 34     | 31.4     | 34          | 97.8     |

| lal                  | 26     | 19      | 77      | 57      | 24.2     | 57     | 24.9     | 59          | 127.4    |

| term1                | 34     | 10      | 734     | 82      | 74.2     | 200    | 82.1     | 83          | 187.2    |

| ttt2                 | 24     | 21      | 179     | 106     | 25.0     | 139    | 31.2     | 140         | 126.3    |

| x3                   | 135    | 99      | 2154    | 497     | 1185.2   | 1942   | 547.0    | 1677        | 2532.9   |

| z4ml                 | 7      | 4       | 13      | 13      | 2.4      | 13     | 21.7     | 13          | 154.1    |

Table 3.1: Experimental results of variable re-ordering.

Figure 3.13: Bina.

element. We show a notation of Bina in Fig. 3.13. If a clock pulse is input to *clk* after input of a pulse to *data*, a pulse is generated at *out*. Similarly, if a clock pulse is input to *clk* after input of a pulse to  $\overline{data}$ , a pulse is generated at  $\overline{out}$ . A set of BDDs is constructed by given logic functions and the set of BDDs are merged. Then, each node of the merged BDDs is replaced by Bina one by one. As an example, we show a full adder with Binas[20] in Fig. 3.14. There are 4 Binas in the circuit. On the other hand, we can construct a full adder with only 2 2x2-Joins (Fig. 3.3). Furthermore, a 2x2-Join cell included in the SFQ cell library[5] consists of 20 JJs in comparison with 27 JJs of a Binas. A 2x2-Join is a

Figure 3.14: A full adder using Binas.

smaller logic element than a Bina.

In [24], a Transduction-based method was proposed as another method of logic synthesis for dual-rail SFQ circuits with  $2\times 2$ -Joins. In the design method, a new logic element called 2x2-AND/XOR[24] shown in Fig. 3.15 is constructed from a 2x2-Join and initial circuits are constructed by the 2x2-AND/XOR. Then, the circuits are optimized by using a transformation-based heuristic method based on the Transduction Method.

We have compared the proposed method with the above methods. In [20], a merging method of BDDs is not described. We have used the constructing method of RSBDDs for merging BDDs. We show the experimental results in Table 3.2. The numbers of  $2 \times 2$ -Joins of the method in [24] is the values described in [24].

From the experimental results, our method can synthesize circuits with fewer  $2 \times 2$ -

Figure 3.15: 2x2-AND/XOR.

|         |        |         | our method          |      |      | method   | ratio (%)           | method   |         |

|---------|--------|---------|---------------------|------|------|----------|---------------------|----------|---------|

| circuit | # of   | # of    |                     |      |      |          | in [24]             | (our $/$ | in [20] |

| name    | inputs | outputs | # of                | # of | # of | CPU      | # of                | in [24]) | # of    |

|         |        |         | $2 \times 2$ -Joins | CBs  | SPLs | time (s) | $2 \times 2$ -Joins |          | Binas   |

| alu2    | 10     | 6       | 144                 | 1013 | 1287 | 10.9     | 236                 | 61.0     | 147     |

| alu4    | 14     | 8       | 349                 | 3170 | 3850 | 123.9    | 479                 | 72.9     | 352     |

| cmb     | 16     | 4       | 25                  | 26   | 50   | 7.2      | 25                  | 100.0    | 26      |

| f51m    | 8      | 8       | 29                  | 131  | 177  | 4.3      | 64                  | 45.3     | 34      |

| lal     | 26     | 19      | 54                  | 101  | 193  | 25.9     | 61                  | 88.5     | 54      |

| term1   | 34     | 10      | 78                  | 202  | 306  | 77.3     | 116                 | 67.2     | 79      |

| ttt2    | 24     | 21      | 103                 | 274  | 472  | 30.8     | 127                 | 81.1     | 104     |

| x3      | 135    | 99      | 494                 | 1406 | 2322 | 1320.1   | 548                 | 90.1     | 494     |

| z4ml    | 7      | 4       | 6                   | 18   | 12   | 2.8      | 12                  | 50.0     | 12      |

Table 3.2: Experimental results of logic synthesis.

Joins than the method in [24]. We can synthesize a circuit with only 45.3% of the number of  $2\times 2$ -Joins in the best case and with 72.9% on average. Furthermore, our method can synthesize circuits with slightly fewer logic elements than the method in [20]. By using our method, we can synthesize small-area dual-rail SFQ circuits. Most of the execution time of our method is expended in reduction of the size of RSBDDs. Once we can obtain reduced RSBDDs, we can synthesize circuits fast.

# 3.6 Summary of the Chapter

We have proposed a new method of logic synthesis for dual-rail SFQ digital circuits. In the method, we construct a root-shared binary decision diagram (RSBDD) from given logic functions and reduce the size of the constructed RSBDD by a variable re-ordering technique. Then, we construct a dual-rail SFQ circuit using the reduced RSBDD. We have implemented the proposed method and have synthesized some benchmark circuits. The experimental results show that the proposed method can synthesize dual-rail SFQ digital circuits which consist of about 27.1% fewer logic elements than those synthesized by a Transduction-based method.

Using the proposed method, we can design small-area dual-rail SFQ digital circuits. This study is a valuable step for CAD systems using dual-rail representation.

# Chapter 4

# Clock Scheduling for Synchronous Clocking SFQ Digital Circuits

# 4.1 Introduction